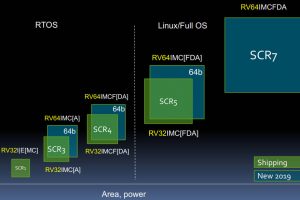

Taiwanese IP provider Andes Technology is offering RISC-V cores, acceleration hardware and development tools. Amongst planned cores is a free one. “With ‘Fast start’ into Risc-V, we will not only introduce our free starter, commercial grade core but also show which other options available, ranging from an ultra-low power MCU over a low power medium-sized Core up to Linux-capable multi-core processors ...

EDA and IP

Adaptable, flexible and open source: the wish list for young engineers

The working practices of today’s young engineers are very much on Victor Peng’s mind. The president and CEO of Xilinx explained why the company’s Vitis, the software platform announced at the Xilinx Developers’ Forum in San Jose, California. He conceded that the company has not normally been associated with open source products. Now it is offering Vitis. “The new generation ...

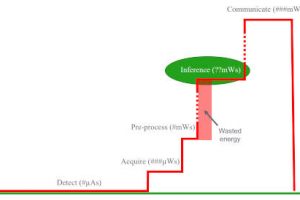

Risc-V day: Greenwaves’ pushes AI to the very edge of IoT

GAP 8 is an ultra-low-power Risc-V AI processor from Grenoble-based GreenWaves, aimed at inferencing (executing already-trained neural networks) inside battery-operated IoT sensors. “Battery-operated sensors have, until now, been restricted to simple data sources such as temperature and humidity,” according to the firm. “But there is increasing interest in processing richer data sources such as images, sounds, and vibrations. These applications require ...

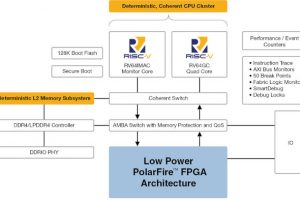

Risc-V day: Microchip adds Risc-V hard IP to PolarFire FPGAs

Microchip detailed an FPGA family with a quad core 64bit RISC-V processor alongside the programmable array. Called ‘PolarFire SoC’, the “architecture brings real-time deterministic asymmetric multiprocessing capability to Linux platforms in a multi-core coherent CPU cluster”, according to the firm, which worked with Risc-V specialist SiFive to create the devices. Real-time operation is included for safety-critical, system control and trusted ...

Xilinx puts new life into HTC and AI development

Xilinx embraces open source community and introduces the Vitis software platform for hardware and software development. At this year’s Xilinx Developers Forum, the company introduced the Vitis software platform, which tailors the hardware architecture to the software of algorithm code without intervention. President and CEO, Victor Peng, explained that the unified platform was developed to “empower software developers, with the ...

Risc-V day: Syntacore for Risc-V MCU core IP

Syntacore has been developing processor core IP based around the Risc-V instruction set for four years

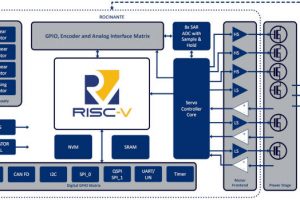

Risc-V day: Trinamic Rocinante motor drive

Trinamic described why it had chosen Risc-V over other processor architectures for Rocinante

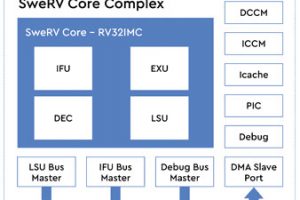

Risc-V day: Western Digital SweRV Core

Western Digital SweRV Core EHX1 is a 32-bit, 2-way superscalar, 9-stage pipeline core, originally designed to be used inside the firms data storage own products. Currently at version 1.1, it is open-sourced for the RISC-V community and, based on internal testing, is expected to deliver up to 4.9 CoreMarks/Mhz. “It offers capabilities for embedded devices supporting data-intensive edge applications, such ...

First silicon for Flex Logix validation chip

Flex Logix says it has received working first silicon of its validation chip for the EFLX 4K eFPGA IP

Moortec In-Chip Monitoring IP on TSMC 5nm

Moortec has availability of its latest In-Chip Monitoring IP Subsystem on TSMC’s N5 and N5P process technologies. A global acceleration in cutting-edge technologies including 5G, Artificial Intelligence (AI), Machine Learning and Data Centre High Performance Computing is fuelling the demand on TSMC’s 5nm FinFET process technology. Such devices are required to operate at the highest level in terms of power, ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News