Cadence Design Systems continues to address the issue of signoff of complex chip designs with a tool which allows for power analysis earlier in the design cycle. Following the introduction of its Tempus timing signoff tool earlier this year, Cadence has announced the Voltus IC Power Integrity tool which, when combined with other package, PCB and system tools, allows designers to address power management issues ...

EDA and IP

Cadence provides interconnect verification tool for ARM-based chips

Cadence Design Systems has introduced a software tool which can provide cycle-accurate analysis of interconnects in the design of ARM-based system-on-chip (SoC) devices. Called Interconnect Workbench, teh tool can be used to identify design issues under critical traffic conditions, and it can be used in conjunction with Cadence Interconnect Validator and a complete suite of AMBA Verification IP for functional ...

Altium cuts cost of ARM Cortex-M MCU based design

Altium has introduced a rapid software prototyping and development platform for ARM Cortex-M based microcontrollers. Pricing starts at $1,795 for the standard edition. The Software Platform will be seen for the first time at the ARM TechCon Conference. It includes a range of middleware functionalities, such as an RTOS, CAN, USB, TCP/IP, I2C, HTTP(S), file systems, graphical user interface, and ...

Hardware emulators work at the system-level, says Mentor

Mentor Graphics introduced earlier this year a hardware emulation platform for ARM Cortex-A9 MPCore processor-based system-on-chip (SoC) device designs. Called isolve, this platform will be used to test embedded designs containing ARM Cortex-A9 dual core processors. At the heart of this system is the EDA firm’s Veloce2 emulator. This is an example of how emulators are changing the economics of ...

Imec works with Delft University on 3D IC design flow tool

Delft University of Technology (TU Delft) and Imec have introduced a test flow cost modeling tool for 2.5/3D stacked ICs. Called 3D-COSTAR, the tool uses input parameters that cover the entire 2.5D-/3D-SIC production flow from design and manufacturing to packaging and logistics. “It is aware of the stack build-up (2.5D versus 3D, multiple towers; face-to-face or face-to-back) and stacking process (die-to-die, die-to-wafer, or wafer-to-wafer). The tool ...

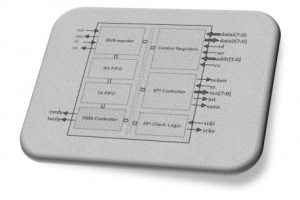

SPI FIFO can configure serial clock signal

Digital Core Design, the Poland-based IP core design house, has developed the DSPI_FIFO, a fully configurable SPI master/slave device, which allows the SoC designer to configure polarity and phase of a serial clock signal SCK. The core enables microcontroller to communicate with serial peripheral devices, but also to communicate with an interprocessor in a multi-master system. It supports all the ...

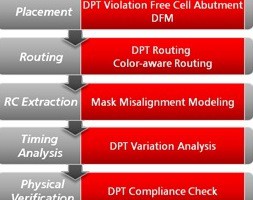

TSMC validates Mentor tools for 3D stacking

TSMC has validated Mentor Graphics design tools for its 3D-IC design flow which implements through-silicon via (TSV)-based 3D stacking of semiconductor die. TSMC’s 3D-IC design flow incorporates capabilities for metal routing and bump implementation, multi-chip physical verification and connectivity checking, chip interface and TSV parasitics extraction, thermal simulation, and comprehensive pre- and post-package testing. Mentor’s Olympus-SoC place and route tool implements physical design for both ...

Make changes to your PCB layout on an iPad

PCB design can now be done on a smartphone or tablet. Zuken has launched a PCB design app that allows designers to access and change layouts using their own tablet or smartphone. The CADSTAR Touch App for iOS or Android can be used to control Zuken’s CADSTAR expert desktop PCB design software, giving simultaneous control of view and program functions. The free app is ...

MathWorks adds to MATLAB and Simulink design tools

MathWorks has announced Release 2013b of its MATLAB and Simulink design and analysis tools. R2013b delivers new analysis, design, code generation and implementation and other features in MATLAB and Simulink, two new Polyspace products, as well as updates to 79 other products. There are two new Polyspace analysis tools for proving the absence of run-time errors in software and for identifying software defects via static analysis. For ...

Vector Software test supports multicore RTOS from Green Hills

Vector Software, the embedded software test specialist, has extended support for the multicore real-time operating systems from Green Hills Software. VectorCAST’s multiprocessing support applies to the entire family of Green Hills’ operating systems, from the standard INTEGRITY to INTEGRITY-178B and INTEGRITY-178 tuMP. This includes support for all multicore architecture configurations currently supported by Green Hills Software. The multicore operating systems support both ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News