This month features the challenge of a battery management system for portable devices, which comes up in PAG Limited’s GB patent. Michael Jaeger, of UK patent and trade mark attorneys Withers & Rogers LLP, writes:

EDA and IP

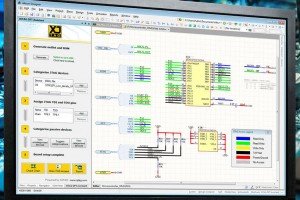

Tool tests JTAG coverage for PCB designers

Boundary scan chain integrity can be checked automatically on Altium’s Designer schematic capture and PCB layout software, using an extension from Cambridge-based XJTAG. Called XJTAG DFT Assistant, and downloadable for free, it “provides engineers with an extension to check if boundary scan chains are correctly connected and terminated at the schematic capture stage, long before the PCB is produced,” said ...

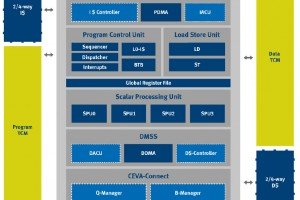

MWC: Ceva baseband processor for 1Gbit/s LTE phones

Full LTE carrier aggregation and simultaneous 3G working, and 5G operation, will be possible with its latest 16Goperation/s baseband control processor, said intellectual property firm Ceva at its launch. Like ARM, Ceva is purely an intellectual property (IP) firm which does not sell silicon. Its main products are baseband PHY DSPs – it claims to have IP in every third ...

Micrium brings “no-cost” RTOS to maker community

Micrium has started to target its µC/OS real-time operating system at maker projects and smaller start-up developments, offering the commercial RTOS to them at no cost. µC/OS for Makers comes with sample design projects and support videos. µC/OS can also be used in safety-critical designs for industries, such as medical electronics, avionics and industrial products. According to Jean Labrosse, president ...

UltraSOC and Lauterbach collaborate for SOC debug

UltraSoC and Lauterbach are collaborating to create a fully-featured independent SoC development and debug environment. The partnership brings together Lauterbach’s TRACE32 integrated, universal development system and UltraSoC’s on-chip debug and analytics IP, to ease the work of engineering teams creating advanced SoCs. TRACE32 is a set of modular embedded development tools with integrated debug environments that support all of the ...

Cambridge firm has IP to test Google VP9 codec standard

Argon Design, a Cambridge-based developer of video compression chip test technology, has signed a licensing agreement with Renesas Electronics. It involves IP for compliance testing to Google’s VP9 codec standard. Argon Streams VP9 is a set of conformance test bit-streams providing full coverage and verification of VP9 video decoders. The bit-streams are derived directly from Google’s VP9 Reference Code using ...

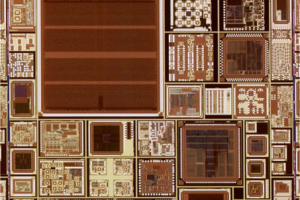

Asic design doesn’t need to be a rich man’s game

Dedicated ASIC design can be cost-effective with the availability of production capacity, tools and lower mask costs, write Nicolas Williams and Jeff Miller Anecdotal mentions of hefty sums of more than $25m just to buy one mask set and total design costs reaching into many hundred million dollars, seem to mark out ASIC design as a rich person’s game. But these ...

Verification is key as automotive chip design goes 28nm

IC design house Sondrel says that automotive SoC design is now starting to focus around the 28nm process node. This is now a well-established and high yield node and so will support the automotive sector’s need for dielectric isolation (leakage current v speed trade off). This will mean that IC designers must address the design rules associated with: High Temperature ...

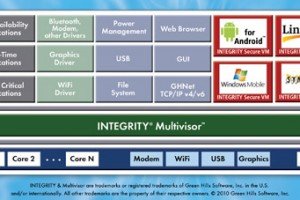

Green Hills adds security to 64-bit ARM and Intel processors

Green Hills Software is offering a real-time, fast-boot platform for securely combining consumer operating systems such as Linux, QNX, Android or Windows with safety- and security-critical software on 64-bit multicore processors. Based on the supplier’s Integrity real-time operating system, the Multivisor virtualisation platform supports both ARM and Intel 64-bit architectures. Green Hills Software’s secure virtualisation platform is being used automotive, ...

Move over Moore’s Law, analogue is key

Move over, Moore’s Law, meet the new market drivers, writes Ravi Subramanian, general manager, analogue and mixed-signal business, Mentor Graphics.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News