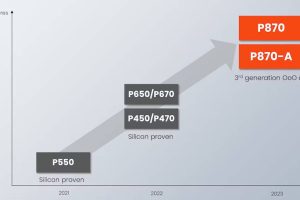

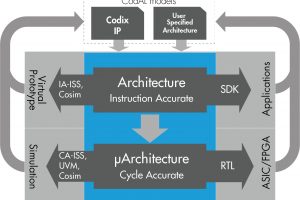

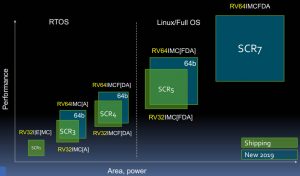

These range from the compact SCR1 MCU core, introduced in 2017 and available free, to the high-performance Linux-capable multi-core 64bit SCR7.

SCR1 executes the RV32I|E[MC] instruction set and can be implemented with 2-4 pipeline stages. It has optional interrupt contol, debug control and multiply-divide unit, and is open-sourced under SHL-license (Apache 2.0 derivative) with unrestricted commercial use allowed. Its minimal (RV32EC) configuration has 11,000 gates, the default configuration (RV32IMC) has 32,000 and it can go above 40,000. Over 250MHz opetration can be expected on TSMC’s 90nm low-power process.

“More than 20 companies are doing something with this core,” said Syntacore engineer Ivan Piatak

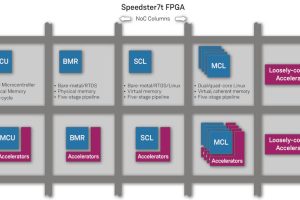

Skipping the intermediate cores (see chart), the SCR7 implements the RV64GC Risc-V and can be configured with up to eight cores (16 to follow). Pipelines can span 10-12 stages, there is decode and dispatch of up to two instruction/cycle, out-of-order issue of up to four micro-op, out-of-order completion and in-order retirement. Virtual memory is supported by a MMU, and there is 16-64kbyte L1 cache and up to 2Mbyte of L2 cache with ECC. >1.2GHz+ operation is expected on a 28nm process.

“Different cores can be used together in heterogeneous multi-core clusters with atomics and memory coherency, according to Piatak. “The cores deliver competitive performance at low power already in baseline configurations, and on top, Syntacore provides a workload-specific processor customisation service for significant performance and efficiency boost.”

As example of customisation, Piatak listed: accelerators for computationally intensive algorithms acceleration, specialised processors such as DSPs, and high-throughput hardware for fast comms interfaces.

For integration with existing designs, the cores support industry-standard interfaces including AHB, AXI4 and ACE.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News