Flex Logix says it has received working first silicon of its validation chip for the EFLX 4K eFPGA IP cores running on GLOBALFOUNDRIES (GF) 12nm Leading-Performance (12LP) FinFET platform and newly announced 12LP+ solution.

Flex Logix says it has received working first silicon of its validation chip for the EFLX 4K eFPGA IP cores running on GLOBALFOUNDRIES (GF) 12nm Leading-Performance (12LP) FinFET platform and newly announced 12LP+ solution.

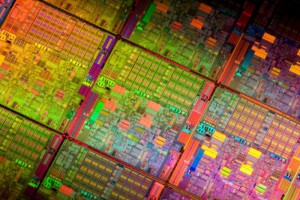

A validation chip consisting of 4 EFLX cores (2 DSP and 2 Logic, for a total of 14K LUT4s and 80 DSP MACs) with integrated RAM has been fabricated and is fully functional at GHz speeds.

The chip is part-way through a full suite of characterization over process, temperature and voltage, and a validation report will be available shortly.

EFLX evaluation boards on GF’s 12LP/12LP+ and 14nm Low Power Plus (14LPP) platform are available now for customers to run their RTL at full speed using on-chip PLLs and RAMs to verify performance and power.

“Flex Logix already has multiple licensed customers for EFLX on GF’s 12/14nm FinFET platforms with several in design, one who has already completed a risk tape-out, and many more in evaluation,” said Geoff Tate, CEO and co-founder of Flex Logix (pictured), “these customers benefit from the ability to have reconfigurable accelerators for critical workloads or for updating changing algorithms and protocols. This is particularly important in aerospace and communications applications where customers need the ability to accelerate critical workloads and reconfigure for changing algorithms and customer needs.”

While the Flex Logix validation chip was fabricated in GF’s 14LPP, the GDS is also compatible with GF’s 12LP and 12LP+ because the design was done with GF standard cells and register files.

The evaluation boards will be available for customers for short-term evaluation or for purchase. All boards come with documentation, examples, test benches and the EFLX Compiler.

The EFLX4K is based on Flex Logix’s Gen 2 architecture, which includes 6-input-LUTs, an improved interconnect for large-array performance, greater MAC pipelining, special logic for test acceleration, and configuration readback.

The Gen 2 architecture has been implemented on multiple processes from 180nm to 12nm, all of which are supported by the same EFLX Compiler software tool.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News