Amongst planned cores is a free one. “With ‘Fast start’ into Risc-V, we will not only introduce our free starter, commercial grade core but also show which other options available, ranging from an ultra-low power MCU over a low power medium-sized Core up to Linux-capable multi-core processors based on RISC-V,” said Andes technical manager Florian Wohlrab.

Branded ‘AndeStar V5’, its cores are:

- N22

2-stage single-issue pipeline

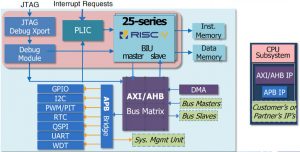

700MHz, 3.95CoreMark and 1.80DMIPS - xx25 devices (see chart)

5-stage single-issue pipeline

>1.2GHz, 3.58CoreMark, 2.09DMIPS

Within N22 is IP with options on the RV32-IMAC or RV32-EMAC instruction set plus Andes own instructions and a configurable multiplier, as well as options on branch prediction, I cache and Local Memory. There is a configurable multiplier, and the bus interface is AHB-Lite (optional APB).

Access options include the FreeStart evaluation program (FSEP) and FreeStart mass-production program (FSMP).

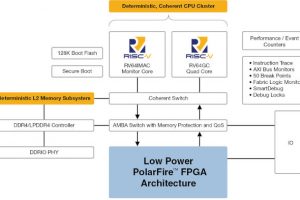

The 25 architecture has RV32/RV64-IMAC instructins plus the firms extensions and configurable multiplier, then optional:

The 25 architecture has RV32/RV64-IMAC instructins plus the firms extensions and configurable multiplier, then optional:

- single or double precision floating point unit

- DSP/SIMD instructions

- memory management

- user-level interrupt

- branch prediction

- I/D caches and local memory

parity or ECC protection

Hit-under-miss caches

HW unaligned load/store accesses - Bus interface

master port (AHB/AXI)

optional slave port (AHB)

The DSP/SIMD extensions were developed by Andes and it has now contributed then to the Risc-V community as the P-Extension draft for 32bit (RV32P) and 64bit (RV64P). They are designed to accelerate audio, voice and slow video, as well as low data rate DSP workloads – the DSP is optimised for low-power and small-area, while the vector extension uses more area and power for more performance.

On a 32bit AMR voice codec, for example, a 5.36x speed-up is claimed when using the extension.

For customers wishing to create their own instructions, there is ‘Andes custom extension’ (ACE), which is a toolset that guides the creation of custom scalar, vector and background instructions.

“ACE lets designers design their own CPU instructions on the already performance optimised processors,” according to the firm. “With ACE instructions designed specifically for the target applications, they can eliminate the software bottlenecks and significantly improve run-time performances.”

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News