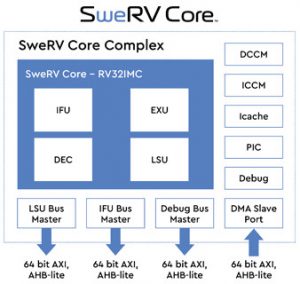

Currently at version 1.1, it is open-sourced for the RISC-V community and, based on internal testing, is expected to deliver up to 4.9 CoreMarks/Mhz.

“It offers capabilities for embedded devices supporting data-intensive edge applications, such as storage controllers, industrial IoT, real-time analytics in surveillance systems, and other smart systems”, according to the firm.

Without RAM, it has a footprint of 0.132mm2 and is expected to clock at up to 1.8GHhz on 28nm CMOS, and run at under 1V, with power dominated by peripheals.

“Is someone is interested in using SweRV Core, we have an FPGA design on GitHub,” Western Digital’s Ted Marena told the London ‘Getting started with Risc-V’ seminar, held on 26 September.

‘SweRV ISS’ instruction set simulator is also available, with test bench support for validation of RISC-V cores.

“This open-source ISS was developed independently from the SweRV Core to ensure RISC-V cores are executing instructions properly,” according to Western Digital. “SweRV ISS models closely coupled memories, caches, interrupts and more. It was used to simulate and validate the SweRV Core, with more than 10 billion instructions executed.”

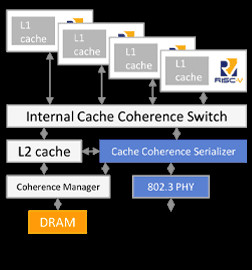

A third product from the firm is OmniXtend, an open approach to providing cache coherent memory over an Ethernet fabric created with Barefoot Network. “This memory-centric system architecture provides open standard interfaces for access and data sharing across processors, machine learning accelerators, GPUs, FPGAs and other components,” according to Western. “It is a truly open solution for efficiently attaching persistent memory to processors and offers potential support of future advanced fabrics that connect compute, storage, memory and I/O components.”

It starts with an open cache coherency bus – available with RISC-V – which is serialised over Ethernet enables a fabric to be possible.

Moran was also representing the Chips Alliance at the London seminar. This is an industry body dedicated to taking the Risc-V instruction set (maintained by the Risc-V Foundation) and designing high-quality RTL to execute it.

Chips Alliance members include Western Digital, Googlr, SiFive, Imperas and Esperanto, and now Alibaba the on-line market place.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News