CHIPS Alliance has announced enhancements to the RISC-V SweRV Core EH2 and SweRV Core EL2, developed for the open-source community by Western Digital. Since the introduction of the cores earlier this year, the CHIPS Alliance has worked with its community to validate the cores through a transparent and rigorous process, as well as incorporate a variety of new updates. The ...

EDA and IP

PLS Universal Debug Engine supports SafeRTOS for safety critical applications

PLS Programmierbare Logik & Systeme has expanded its Universal Debug Engine (UDE) to cover the SafeRTOS real-time operating system. UDE is intended for debugging, testing and analysing microcontroller applications, and this addition gives it functions software development of real-time and safety-critical applications. SafeRTOS is a pre-emptive, safety critical RTOS from Wittenstein High Integrity Systems, available pre-certified by TÜV SÜD to ...

Hardware blocks chip hacking by analogue attack

UltraSoC and Agile Analog have teamed-up to deliver hardware-based security against ‘analogue interference’ attacks such as power supply or clock signal tampering. The aim is to combining UltraSoC’s embedded on-chip analytics with Agile Analog’s on-chip analogue monitoring IP. As well as voltage and clock glitching, these side-channel attacks can also include deliberate brown-outs and temperature variations, all to gain access to ...

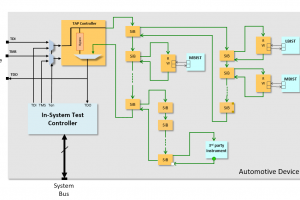

Sponsored Content: Leveraging Runtime Monitoring and Management for Automotive Functional Safety

The promise of autonomous vehicles is driving profound changes in the design and testing of automotive semiconductor parts, writes Lee Harrison, Automotive IC Test Solutions Manager, Tessent Group – Mentor, a Siemens Business. Automotive ICs are increasingly developed and manufactured using cutting-edge processes. These devices are no longer only deployed for simple functions like controlling windows or light signaling but ...

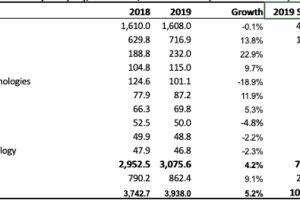

Q4 EDA revenues up 2.2% y-o-y

Q4 EDA revenues rose 2.2% y-o-y to $2.626 billion, according to the Electronic System Design (ESD) Alliance Market Statistics Service (MSS). Q4 2018 revenues were $2.57 billion. Full year 2019 revenues were $10.2 billion which was 8.3% up on 2018. “The EDA industry reported increased revenue in Q4 compared to Q4 2018, in part due to strong growth in Europe, ...

Silicon Integration Initiative adopts compact model for FD-SoI

The Compact Model Coalition (CMC) has adopted a model from French lab Leti for fully-depleted silicon-on-insulator (FD-SoI) chip simulation. Called L-UTSOI, it was “proven by the industry and its standardisation will ensure long-term access and maintenance in EDA tools for FD-SOI designers”, according to Leti. Available to Coalition members now, it will be implemented in major versions of circuit-simulation software, and its ...

Arm down in an up market

Arm’s revenues declined slightly in 2019 in a market that grew, says IPnest, reflecting similar situations in 2018 and 2017. Arm’s royalty revenue declined by 6-7%, says IPnest, but its licensing revenues – including physical IP – were up 13%. Companies ranked by semiconductor design IP revenue in 2019 (millions of dollars). Source: IPnest (March 2020). ARM once controlled 50% ...

Neural net accelerates IC design placement

Google has come up with a neural net that can do IC design placement in record quick time.

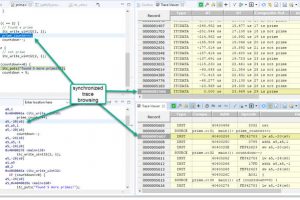

Trace and debug for RISC-V IP

SiFive has announced hardware trace and debug for RISC-V processor IP. Called SiFive Insight, it is intended to, according to the company, “meet customer demand and expectations for the capability to access, observe, and control products deploying SiFive’s RISC-V Core IP portfolio”. “SiFive Insight is the industry’s first integrated RISC-V processor core, trace, and debug IP solution from a single ...

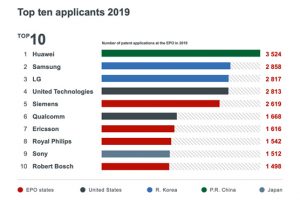

Huawei tops EPO patent filers list for 2019

The European Patent Office has released a list of the top patent filers for last year.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News