STMicroelectronics has introduced an all-in-one multi-OS software tool for programming its Arm-based STM32 products. From now on, new STM32 products will be supported only the tool, to be called STM32CubeProg, so it obsoletes existing tools including: ST Visual Programmer (STVP) DFuSe USB Device Firmware Upgrade programmer Windows-only STM32 Flash loader software utilities for use with ST-Link STM32CubeProg (or STM32CubeProgrammer, ST ...

EDA and IP

Bridgetek expands EVE graphics chip toolchain

Bridgetek has broadened the human-machine interface (HMI) development toolchain that accompanies its Embedded Video Engine (EVE) product portfolio. Several extra elements have been added, and there are upgrades to the existing tools. A core aspect of this toolchain is the EVE Asset Builder (EAB). This conversion utility is said to make HMI construction much more straightforward and save considerable time, ...

Achronix turns to UK for on-die temperature sensing

US fast FPGA maker Achronix has chosen Moortec’s 7nm embedded temperature sensor intellectual property for integration into its Speedster7t FPGAs. Based in Plymouth, Moortec is a provider of on-die PVT (process, voltage, temperature) monitoring sub-systems. “Achronix chose to use Moortec’s 7nm embedded in-chip temperature sensor in our Speedster7t FPGA devices based on their accuracy and advanced features,” said Acronix‘ v-p ...

OpenHW to boost adoption of open source processors

OpenHW is a not-for-profit organization aimed at boosting the adoption of open-source processors by providing a platform for collaboration, creating a focal point for ecosystem development, and offering open-source IP for processor cores. Headed by Founder and CEO, Rick O’Connor (pictured), the OpenHW Group has already recruited 13 sponsor organizations and expects this to grow to 25 by the end ...

Analog Bits IP on GloFo 12nm

Analog Bits has put its analogue and mixed signal IP design kits on Globalfoundries’ 12nm Leading-Performance (12LP) process technology. The IP portfolio includes wide range fractional Phase-Lock Loop (PLL) with Spread Spectrum Clock Generation (SSCG), PCIe reference clock PLL subsystem, Process, Voltage, and Temperature (PVT) Sensor and Power-On-Reset (POR) circuitry. Silicon Reports based on these IPs will be available 2Q ...

Arm gives up control of IP to China

Arm has given up control of its technology to China, reports the Nikkei. A joint venture called Arm mini China – which is 51% owned by Chinese interests, principally the Hou-An Innovation Fund – has taken control of licensing Arm IP to Chinese companies. “With this joint-venture, China expects to secure sources of technology, especially for some sensitive chips that ...

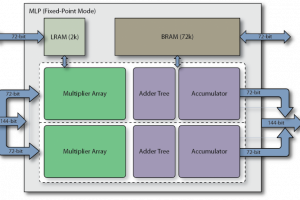

Cadence machine can prototype a 1bn gate SoC on FPGAs

For software development without final silicon, Cadence has launched FPGA-based hardware that can simulate SoCs with up to a billion gates. Called Protium X1, it is intended for debugging software intended to run on SoCs that have yet to be fabbed – for AI, 5G mobile and graphics processors, for example. It can run a 1bn gate design at around 5MHz, ...

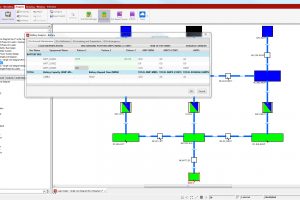

Analyser software uses digital twin for aero certification

Software developed by Mentor is designed to help aircraft projects meet electrical load compliance. The Capital Load Analyzer software reduces risk in aerospace electrical compliance and certification. Anthony Nicoli, IES director of Aerospace and Defense, Mentor explained that the increased information and displays used in the aircraft cockpit for flight control and in passenger in-flight entertainment systems, has increased the ...

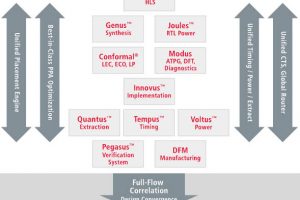

Cadence design and sign-of tools for 7nm Arm Cortex-A77

Cadence has announced design and sign-off tools for Arm’s new Cortex-A77 CPU on 7nm processes. The 7nm rapid adoption kit (RAK) provides an RTL-to-GDS flow using Arm 7nm POP IP libraries. “We worked with Arm to optimise our digital implementation and sign-off solutions for the Cortex-A77 so customers can create 7nm designs that meet PPA [power, performance and area] goals,” ...

Toolchain supports RISC-V cores

Swedish embedded software provider, IAR Systems, has recognised the increased adoption of RISC-V-based designs, with the introduction of a C/C++ compiler and debugger toolchain to support RISC-V cores. The first version of IAR Embedded Workbench for RISC-V has been internally tested and the company reports that the C/C++ compiler improves code density, compared to other tools currently available, generating code that ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News