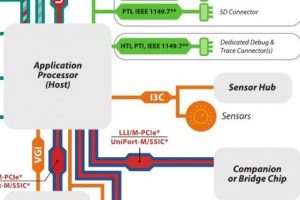

The MIPI mobile interface organisation is opening access to its sensor interface specification, called MIPI I3C.

EDA and IP

Cruden simplifies hardware driving simulator design

Dutch firm Cruden has developed a simulation tool for automotive R&D that combines hardware-in-the-loop (HIL) set-ups and driver-in-the-loop (DIL) simulators. As an example, Cruden installed a driver simulator merged with a dSPACE HIL set-up at the Ostfalia University of Applied Sciences in Germany, where students can integrate hardware into the driving simulator. HIL set-ups, for testing sensors, controllers and actuators ...

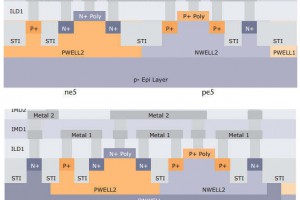

Updated: X-FAB adds to low-noise transistor portfolio

X-FAB has added three new low-noise transistors to its 180nm process node: a 1.8 V low-noise NMOS, a 3.3 V low-noise NMOS and a 3.3 V low-noise PMOS – all of which offer drastically reduced flicker noise compared to standard CMOS offerings. For transistor specs, see table below These transistors are mainly designed for sensor deployments which require very low-noise signal ...

Green Hills ups spec for safety-critical C/C++ compilers

Green Hills Software is now offering its optimising C and C++ compilers for 32-bit and 64-bit embedded processor architectures, including ARM, Intel and Power Architecture. The Compiler 2017.5 also supports Renesas RH850, MIPS, ColdFire and TriCore embedded processor architectures. Features of the compliers include C/C++ functional safety certification, higher performance and greater compatibility with third-party tools. The C/C++ Compilers 2017.5 are ...

Green Hills adds to secure RTOS support for Xilinx Zynq

Green Hills Software is supporting secure system development on the Zynq UltraScale+ MPSoC from Xilinx with its Integrity real-time operating system (RTOS) and supporting tools. Zynq UltraScale+ integrates 64-bit ARM Cortex-A53 processor cores and an FPGA fabric which is being used in applications for automotive intelligence, industrial vision and defence. The secure RTOS allows software of different levels of criticality to run on the ...

ARM TechCon: Moortec and Sonics offer tight frequency scaling

Moortec has teamed with Sonics, US-based on-chip network firm to provide advanced power management techniques for ARM-based system-on-chip (SoC) and MCU designs. The partnership, announced at ARM TechCon in California, combines Sonics’ ICE-P3 dynamic voltage and frequency scaling technology with Plymouth, UK-based Moortec’s temperature sensors to provide on-chip temperature-compensated, dynamic voltage and frequency scaling. This allows chip designers to reduce ...

Green Hills verifies multicore OS for future airborne systems

Green Hills Software is to verify conformance of its Integrity-178 operating system with the technical standard for Future Airborne Capability Environment (FACE) edition 2.1. Certon, the critical systems certification firm, will help carry out the verification Time-Variant Unified Multi Processing (tuMP) operating system for three different multicore architectures, or Units of Conformance (UoC): Intel, ARMv8 and PowerPC/QorIQ. Integrity-178 is also being verified ...

Denso licenses Cortex-R52 to automated driving

Denso is licensing ARM's Cortex-R52 for automated driving systems and vehicle control reference platforms.

Welsh chip design IP firm gets funding boost

Wales-based analogue IP re-use firm Thalia Design Automation has secured $865k (£640k) funding in its latest round. The firm said it has achieved “significant customer traction within the last 18 months”. Thalia also plans to recruit more analogue IC developers. The company has developed technology for transferring RF, analogue and mixed-signal IP designs to silicon, using its design automation technology. ...

Lauterbach debugger targets 64-bit ARM and Intel chips in cars

Lauterbach is working with QNX to provide JTAG debugging capabilities for the latest QNX Version 7.0 secure embedded OS for the automotive industry.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News