Infineon has announced software support the ‘Matter’ smart home protocol. “Many smart home products use Infineon’s Airoc Wi-Fi, Airoc Bluetooth, and PSoC 6 microcontroller products,” according to the company. “In this regard, support for Matter in Infineon’s ModusToolbox software and tools is an important milestone for the adoption of the emerging standard.” Matter came out of the Zigbee Alliance as it rebranded ...

EDA and IP

Arm offers cloud-based virtual Cortex-M hardware, and a security framework

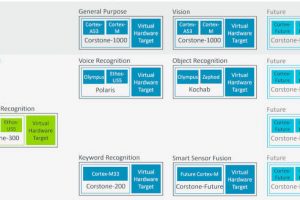

To allow early software development, Arm is offering cloud-based simulation of some of its standard Cortex-M SoC configurations. At the same time, it has created a standards-based model for creating secure IoT devices built around Cortex-M processors. Cloud-based SoC emulation for Cortex-M Dubbed ‘Arm Virtual Hardware’, the cloud-based simulators are aimed at software developers, OEMs and service providers, and will ...

DVCon Europe 2021 announces extra keynotes and a VR format

The Design and Verification Conference and Exhibition (DVCon Europe) takes place on Tuesday and Wednesday 26-27 October and SystemC Evolution Day will be Thursday 28 October. The event, sponsored by Accellera Systems Initiative, the EDA standard organisation, will be a 3D VR environment. Avatars will mingle in a virtual conference centre, with tantalising glimpses of Munich to be seen through ...

Aprisa physical design software upgraded

Siemens Digital’s latest release of its Aprisa physical design software – Aprisa 21.R1 – is now available. Improvements include: • Average full-flow runtime reduction of 30% compared to the previous release, and up to 2X faster runtimes for larger, more challenging designs. • Enhancements to all major place-and-route engines, from placement optimization to clock tree synthesis (CTS) optimization, route optimization ...

Green Hills covers Risc-V with Integrity

Green Hills Software has announced a version of its safety and security-enhanced Integrity real-time operating system for RISC-V. The RTOS is integrated with hardware boards from Microchip (PolarFire Icicle kit) and SiFive (HiFive Unmatched board), processor intellectual property from SiFive and can be used with Microchip’s PolarFireSoC and Mi-V ecosystem. “The integration of safety and security-critical RTOS Integrity into SiFive ...

Cadence announces 3D IC design platform

Cadence has announced what it claims is “industry’s first comprehensive high-capacity 3D IC platform that integrates 3D design planning, implementation and system analysis in a single unified cockpit.” It is called ‘Integrity 3D-IC’ and is said underpin the company’s third-generation 3D IC solution, providing power, performance and area for individual chiplets through integrated thermal, power and static timing analysis capabilities. ...

Security software protects at pre-silicon stage

Pre-silicon security verification during the chip design stage can avoid time-consuming analysis and correction of security vulnerabilities for a manufactured device. It can also avoid potential re-spins and production delays, says FortifyIQ. The company has developed two software suites which simulate some of the ‘popular’ methods of cyberattack. SideChannel Studio simulates side-channel attacks whereby cyber criminals measure physical characteristics, such as power ...

Power integrity software provides full chip analysis

Believed to be the first electromigration/voltage drop (EM/IR) tool for both analogue and digital methodologies, mPower has been released by Siemens Digital Industries. The tool marks Siemens’ entry into the IC power analysis market, capable of power integrity analysis for analogue, digital and mixed-signal IC designs. It is also scalable and uses industry standard inputs and interfaces. Power integrity analysis ...

Synopsys unifies its reliability analysis workflow

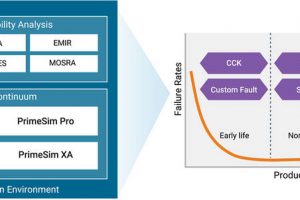

Synopsys has unified the workflow through its existing reliability analysis tools for analogue, mixed-signal and custom IC designs – integrating them into its PrimeWave design environment, along with PrimeSim Continuum that announced in April. The unified workflow is to be called PrimeSim Reliability Analysism and is an umbrella for its CKK, Custom Fault, AVA, SPRES, EMIR and MOSRA tools (see table ...

C++ synthesis suite for PolarFire FPGA algorithm development

Microchip has released a C++ algorithm high-level synthesis design workflow for its PolarFire FPGAs. “A large majority of edge compute, computer vision and industrial control algorithms are developed natively in C++ by developers with little or no knowledge of underlying FPGA hardware,” according to the company. Called SmartHLS, the tool allows C++ algorithms to be directly translated to FPGA-optimised RTL ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News