Kyocera is suing German automotive component supplier Preh for infringement of its haptic feedback patents. The lawsuit, in a Dusseldorf court, says that Kyocera has been creating haptic technologies through its own R&D efforts since 2008. Kyocera says that, utilising ergonomics and virtual reality technology that Kyocera has developed over the years as well as its proprietary haptic feedback technology, Kyocera’s ...

EDA and IP

Silvaco and Silicon Catalyst to provide free IC IP to start-ups

Silvaco and Silicon Catalyst are teaming up to provide silicon proven IP.

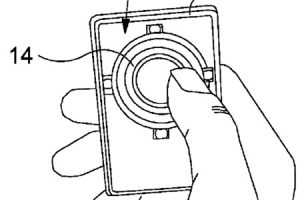

Electronics patent of the month: Avoiding ‘card clash’ when making payments

Featuring a neat, contactless payment device that avoids the problem of card clash by making use of passive NFC technology.

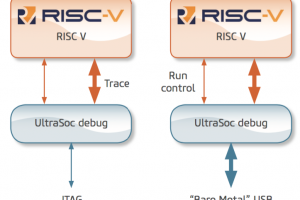

Embedded World: Lauterbach and UltraSoC back RISC-V

Lauterbach and UltraSoC have added support for the RISC-V open-source processor architecture to their joint chip development and debug environment. “Across the industry there is rising excitement about the emergence of RISC-V as an open source processor,” said UltraSoC CEO Rupert Baines. “This is especially significant in heterogeneous multi-core architectures: engineers want the choice to ‘mix and ‘match’ cores and freely ...

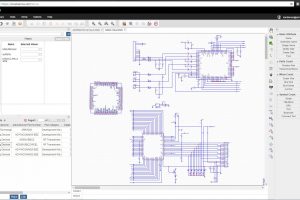

KiCad is big news for schematic capture, says Digi-Key

Digi-Key Electronics has put a new library of nearly 1,000 common parts for use by the open source, KiCad schematic capture and printed circuit board tool on beta release on its website. The distributor has selected the most popular parts for users of KiCad and created a library that links the schematic symbols and printed circuit board footprints. It has ...

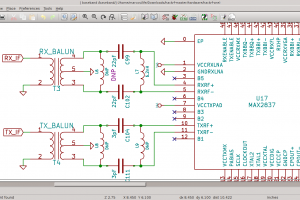

Cadence and Arrow offer cloud-enabled product design

Arrow Electronics and Cadence Design Systems are aiming to support faster product development with the introduction of the Cadence OrCAD Entrepreneur package for OrCAD Capture Cloud in Arrow’s design centre. These are established PCB layout tools, and the association with Arrow provides wider market availability. Matt Anderson, Arrow chief digital officer, writes: “The aim is to help engineers bring their ...

RISC-V processor trace IP available

The open-source RISC-V processor architecture is getting a trace function through an IP (intellectual property) block from Cambridge-based UltraSoC. It supports both 32 and 64-bit RISC-V designs, and is intended to integrate with the firms other RISC-V offerings. “The addition of trace capabilities means that UltraSoC provides the most comprehensive RISC-V commercial debug solution,” claimed the firm. RISC-V processor vendors ...

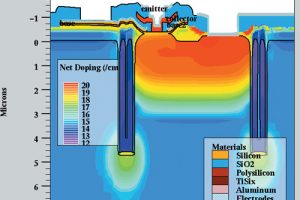

Synopsys buys Kilopass Technology – OTP NVM IP becomes part of DesignWare

EDA and IP company, Synopsys, has bought Kilopass Technology. The antifuse one time programmable (OTP) IP provider’s non volatile memory (NVM) IP has been incorporated into the DesignWare IP portfolio of logic libraries, embedded memories, embedded test, analogue IP, wired and wireless interface IP, security IP, embedded processors and subsystems. The OTP NVM IP for SoC designs, rebranded as DesignWare ...

CEVA algorithms clarify voice input

CEVA has started licensing ClearVox – voice input processing algorithms aimed at enhancing speech intelligibility and voice clarity for the CEVA-TeakLite-4 and CEVA-X2 audio/voice DSPs. Voice-enabled speakers have to cope with multi-mic beamforming, multi-channel acoustic echo cancellation and noise suppression in their products. The ClearVox algorithms cope with different acoustic scenarios and microphone configurations, including optimized software for speaker direction of ...

Moortec opens Gdansk design centre

Moortec, the Plymouth PVT IP company, has opened a design centre in Gdansk (pictured). It will be headed up by Moortec Design Centre Manager, Szymon Gerka. Moortec provides embedded IP subsystem solutions for Process, Voltage & Temperature (PVT) monitoring, targeting advanced node CMOS technologies from 40nm down to 7nm. “The Design Centre in Gdańsk will allow Moortec to accelerate its ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News