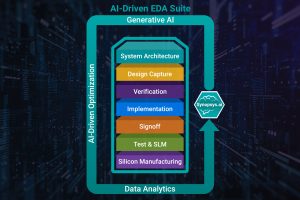

The unified workflow is to be called PrimeSim Reliability Analysism and is an umbrella for its CKK, Custom Fault, AVA, SPRES, EMIR and MOSRA tools (see table below).

“PrimeSim Reliability Analysis solution provides a converged workflow around reliability analysis technologies and PrimeSim Continuum simulators to provide cohesive reliability verification,” Synopsys product director Anand Thiruvengadam told Electronics Weekly.

The package includes conventional and machine learning technologies for high-sigma leaf cell characterisation, static circuit checks, power network integrity, signal network integrity, resistance, EM and IR signoff analysis, MOS aging analysis and safety and test coverage analysis using analogue fault simulation.

| Reliability Analysis element | Description | Lifecycle Stage |

| PrimeSim CCK | Chip-level static analogue and digital circuit checks | Early |

| PrimeSim Custom Fault | Chip-level analogue fault simulation | Early |

| PrimeSim AVA | Machine learning based 6-7σ Monte Carlo analysis for leaf cells | Normal |

| PrimeSim Res Check (SPRES) | Static power and signal net resistance check | Normal |

| PrimeSim EMIR | Dynamic EMIR analysis | End |

| PrimeSim MOSRA | MOS aging analysis | End |

Synopsis foresees use with complex automotive, aerospace, defence, medical and 5G applications.

At the same time as it announced Reliability Analysis, Synopsys said companies including AMD, Dialog, TDK-Micronas and STMicroelectronics are already using it, and said that aspects of it had been certified by TSMC and qualified by Samsung Foundry, Intel or GlobalFoundries.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News