IAR Systems has added support for AndeStar V5 Risc-V Performance Extension to Embedded Workbench for Risc-V. The toolchain supports all 32bit Andes V5 Risc-V cores, including N22, N25F, D25F, A25, A27, N45, D45 and A45. Risc-V Packed SIMD/DSP extension specification (RVP draft) and the corresponding intrinsic functions as well as Andes DSP libraries are supported. “AndeStar V5 offers compatibility to Risc-V technology ...

EDA and IP

Xilinx adds machine learning optimisation to Vivado to accelerate design cycle

Claiming to be able to reduce design compile times by a factor of five, Xilinx has launched the Vivado ML Editions tool suite. The latest addition to the company’s Vivado tool suite is believed to be the first FPGA EDA tool suite based on machine learning (ML) optimisation algorithms. In addition to faster compile times, it is claimed to deliver ...

SiFive’s highest performance Risc-V IP

SiFive has announced its highest performance implementation of a Risc-V core yet. Called the Performance P550, the intellectual property is said to deliver a SPECInt 2006 score of 8.65/GHz, “making it the highest performance Risc-V processor available today, and comparable to existing proprietary solutions in the application processor space” according to the company. April 2024 update: SiFive releases a quad ...

Siemens acquires Supplyframe for a ‘digital transformation’

The recent component shortage has highlighted the fragility of current supply chains, asserted Siemens, as it announced the acquisition of electronics Design-to-Source platform, Supplyframe. The transaction is expected to close at the end of this financial year. The acquisition is part of Siemens’ digital transformation said AJ Incorvaia, senior vice president, Siemens Digital Industries Software, Electronic Board Systems , putting Supplyframe ...

Xilinx acquires Silexica and its C/C++ tools

Xilinx has acquired German C/C++programming tool provider, Silexica. The privately held company produces C/C++ programming and analysis tools for automotive, aerospace and defence, wireless comms, robotic and financial markets. Its SLX FPGA tool suite is used to manage the HLS (high level synthesis) design flow. In February this year, Silexica and Xilinx co-presented at the International Symposium on FPGA, elaborating ...

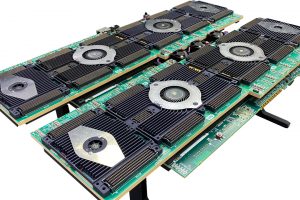

Siemens Digital buys proFPGA prototyping technologies

Siemens Digital Industries Software has bought the proFPGA desktop prototyping technologies product suite from Pro Design Electronic. proFPGA technology is already part of Siemens’ Xcelerstor portfolio as part of its EDA IC verification products. Bringing the proFPGA technology and team in-house can allow Siemens to more fully integrate and optimize the scalable, high-performance prototyping platform for lab and desktop environments ...

Compiler uses C code to write once and accelerate CPUs

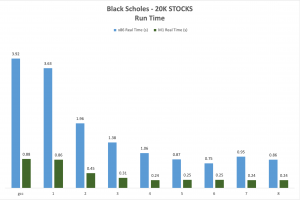

Support for multi-threading acceleration for CPUs with multiple physical cores is provided by the CacheQ Compiler which takes a single-threaded C code and generates executable that can run on CPUs, accelerating executing by 486% on x86 processors with 12 cores, reports CacheQ Systems (based on benchmarks from the Black Scholes financial algorithm). There is no need for manual code rewriting, threading ...

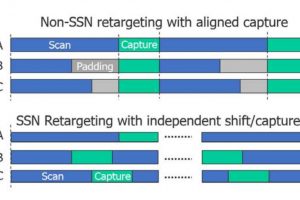

Sponsored Content: Packetize test data for no-compromise DFT

Bus-based scan data distribution architecture enables true bottom-up DFT flows, writes Geir Eide of Siemens Digital Industries Software. The dramatic rise in manufacturing test time for today’s large and complex SoCs is rooted in the use of traditional approaches to moving scan test data from chip-level pins to core-level scan channels. The pin-multiplexing (mux) approach works fine for smaller designs ...

Cadence unveils next generation of transistor-level circuit simulator for verification

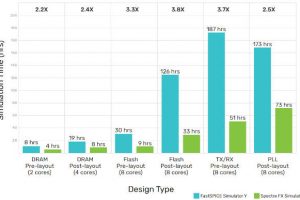

Cadence is claiming up to 3x transient simulation performance for its latest transistor-level circuit simulator, compared with its previous offering. Called Spectre FX Simulator, it is the next generation of the company’s ‘FastSpice’ branded products, aimed at pre and post-layout verification of large DRAM, flash, SRAM and transistor-level SoC designs. “Design teams can verify functionality and timing for sign-off in a productive manner,” according to ...

Machine learning assistance for Infineon PSoCs

Infineon has announced machine learning extensions to its ModusToolbox for deep learning workloads on its PSoC microcontrollers. “Enabled by TinyML, ‘artificial intelligence of things’ is a natural evolution, where acting on data locally helps manage data privacy, latency and overall system reliability,” said Infineon v-p IoT Steve Tateosian. “ModusToolbox bridges a gap between machine learning and embedded systems design by ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News