Axivion has added checks for MISRA C++ 202x rules with the release of its Axivion Suite 7.5 code analysis tools. “Especially when developing safety-critical embedded systems, compliance with the latest coding standards is a must to ensure code quality throughout the whole development process,” according to the company. “Now Axivion Suite 7.5 safeguards compliance with several new MISRA C++ 202x ...

EDA and IP

Digi-Key to match donations for open-source EDA KiCad suite

Digi-Key Electronics has announced that it will match donations made to KiCad, the open-source software EDA suite for Electronic Design Automation. The offer runs from 1-7 December up to a value of $15,000. According to its creators, the goal of KiCad is to provide “the best possible cross-platform electronics design application for professional electronics designers”. It’s aim is to hide ...

Post-quantum cryptographic IP from Xiphera

Xiphera has announced intellectual property cores for implementing hardware post-quantum cryptography security on FPGAs and asics. Such security is executed on classical computing platforms to protect against quantum computing based attacks. Branded ‘xQlave’, the IP blocks are aimed at quantum-secure key exchange and digital signatures. “Powerful enough quantum computers will be able to break current public-key asymmetric cryptosystems based on ...

Simulation model certified for functional safety Risc-V core

Risk-V intellectual property company Andes Technology has certified simulation reference models from Imperas reference for use evaluating multi-core designs featuring the functional-safety-optimised AndesCore N25F-SE. At the same time, it also certified the complete range of Andes processor IP blocks with ‘Andes Custom Extension’ (ACE) support. Such virtual references run exactly the same binary code as any resulting hardware would. “Functional ...

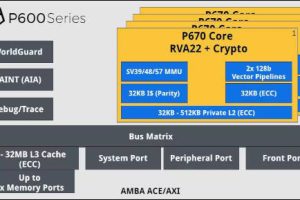

High-performance RISC-V cores from SiFive

SiFive has announced two high-performance RISC-V processing cores. “P670 and P470 are specifically designed for the most demanding workloads for wearables and other advanced consumer applications,” said SiFive v-p Chris Jones. “We have optimised these RISC-V Vector-enabled products to deliver performance and efficiency improvements and we are in evaluations with a number of top-tier customers.” Both are also available in ...

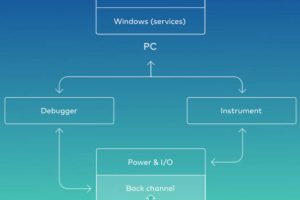

JavaScript tool automates instrumentation for embedded system development

London embedded systems design and test house Bermondsey Electronics has launched what it describes as an “integration verification engine” that automates the operation of networkable instrumentation to exercise a device-under-test (DUT) and verify that its hardware and software are functioning together as intended. Called Believe, and based on JavaScript, it “can also be used for continuous integration and end-of-line quality ...

Cadence: IC design tool speeds sign-off

Cadence has announced a design tool for IC design sign-off. Called Certus closure solution, the “environment automates and accelerates the complete design closure cycle, from sign-off optimisation through routing, static timing analysis and extraction”, said Cadence. “The solution supports the largest chip design projects with unlimited capacity.” It lists these attributes: Distributed hierarchical optimisation and sign-off architecture for cloud and ...

Cadence applies Big Data to AI chip design

Cadence has announced artificial intelligence driven verification applications that use ‘big data’ to “optimise verification workloads, boost coverage and accelerate root cause analysis of bugs”, according to the company. Together called the Verisium platfom, the suits are is built on another of the company’s platforms: JedAI (joint enterprise data and AI). “The release of Verisium represents a generational shift from ...

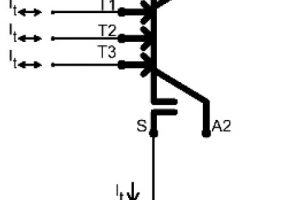

Novel logic aims to beat CMOS, on 10 year older fabs

Nottingham-based SFN (Search for the Next) has characterised its novel transistor-based logic, and claims that it matches CMOS performance even when made in older fabs. It would “enable chip designers to produce ICs in older 180nm, and even one micron, geometry fabs with the equivalent performance of CMOS devices made in state-of-the-art plants”, according to the company. “For example, a ...

Siemens Digital joins RAMP

Siemens Digital Industries Software is to participate in the Rapid Assured Microelectronics Prototypes (RAMP) Phase II initiative. RAMP is a programme established by the US Department of Defense (DoD) to develop secure design and prototyping capabilities to demonstrate how the DoD can securely leverage state-of-the-art microelectronics technologies without depending on a closed-security architecture fabrication process or facility. In 2020, the ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News