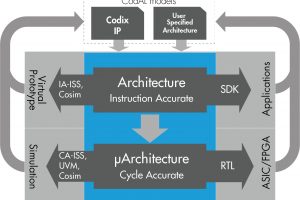

Risk-V intellectual property company Andes Technology has certified simulation reference models from Imperas reference for use evaluating multi-core designs featuring the functional-safety-optimised AndesCore N25F-SE.

At the same time, it also certified the complete range of Andes processor IP blocks with ‘Andes Custom Extension’ (ACE) support.

Such virtual references run exactly the same binary code as any resulting hardware would.

“Functional safety applications demand a high standard of system and software quality which in turn has implications for the project planning, tools and methodology,” according to Imperas. “Functional safety is not just about resolving traditional software bugs and errors but also subjecting the entire platform to exceptional situations and functional stress conditions.”

ACE technology helps users implement custom functions and instructions.

Andes’ AndeSysC environment is a near-cycle-accurate SystemC model library. “With the integration with the Imperas reference models and tools, design teams can embark on architecture exploration with complete application software with a path to ACE implementation,” said Andes CTO Charlie Su. “SoC architects can use it to construct a virtual platform for performance evaluation of critical code segment and hardware/software co-optimisation.”

The Imperas reference models are available though this web page

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News