Together called the Verisium platfom, the suits are is built on another of the company’s platforms: JedAI (joint enterprise data and AI).

“The release of Verisium represents a generational shift from single-run, single-engine algorithms in EDA (electronic design automation) to algorithms that leverage big data and AI to optimise multiple runs of multiple engines across an entire SoC design and verification campaign,” it said. “By deploying the Verisium platform, all verification data, including waveforms, coverage, reports and log files, are brought together in the Cadence JedAI Platform. ML [machine learning] models are built and other proprietary metrics are mined from this data to enable a new class of tools that dramatically improve verification productivity.”

The initial Verisium apps, as described by Cadence, are:

- AutoTriage: Builds ML models that help automate regression failure triage by predicting and classifying test failures with common root

- SemanticDiff: Algorithmic solution to compare multiple source code revisions of an IP or SoC, classify these revisions and rank which updates are most disruptive to the system’s behaviour to help pinpoint potential bug hotspots.

- WaveMiner: AI analyses waveforms from multiple runs and determine which signals, at which times, are most likely to represent the root of a test failure

- PinDown: Builds ML models of source code changes, test reports and log files to predict which source code check-ins are most likely to have introduced failures

- Debug: Delivers a debug solution from IP to SoC and from single-run to multi-run, offering interactive and post-process debug flows with waveform, schematic, driver tracing and SmartLog technologies. It is natively integrated with JedAI and other Verisium apps to enable AI-driven root cause analysis with the support of simultaneous automatic comparison of passing and failing tests

- Manager: Brings Cadence’s IP and SoC-level verification management, with verification planning, job scheduling and multi-engine coverage onto the JedAI, and extends it to support AI-driven test suite optimisation. Integrates with other Verisium apps to deploy Verisium platform from a browser-based console.

JedAI

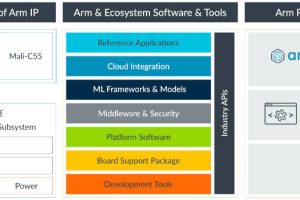

JedAI is intended to glean intelligence from massive volumes of chip design and verification data, and with it Cadence is unifying big data analytics across its AI platforms: Verisium for verification, Cerebrus for implementation and Optimality for system optimisation.

Cadence claims it can manage both structured and unstructured data, including:

- Design data such as waveforms and coverage in functional verification, physical layout shapes, design RTL, netlist and analysis reports for timing, power, voltage or variation

- Workload data such as run-time, memory usage and disc space usage, “as well as metadata about the inputs to each job and dependencies between them”

- Workflow data such as the tools and the methodology used to create a design

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News