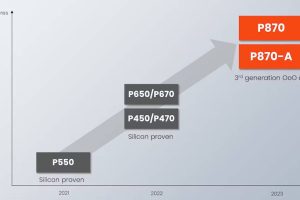

SiFive has announced a pair of high-end RISC-V cores for AI and machine learning in consumer, automotive and infrastructure markets. “Performance P870 and Intelligence X390 offer a new level of low power compute density and vector compute capability, and when combined provide performance for data intensive compute,” according to the company, which is advocating combining the general-purpose scalar P870 with ...

EDA and IP

DVCon Europe celebrates 10th anniversary in Munich in November

DVCon Europe, the Design and Verification Conference & Exhibition Europe, is celebrating its 10th anniversary this year. The event centres on the application of languages, tools and IP for the design and verification of electronic systems and ICs. Two keynote speakers have been confirmed. Philippe Notton, CEO and funder of SiPearl and Michaela Blott, senior fellow at AMD Research (pictured) ...

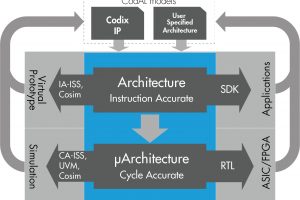

Codasip offers Siemens’ Tessent Enhance Trace Encoder

Codasip, RISC-V Custom Compute specialist, now offers Siemens EDA’s Tessent Enhanced Trace Encoder product with its customisable RISC-V cores, allowing developers to trace and debug issues between silicon and software, and understand real-time behaviour of designs based on Codasip processors System designers can use the Codasip Studio toolchain to find the best software and hardware trade-offs and achieve optimal features ...

Accellera sets the date for multi-domain simulation discussions

In an effort to create and standardise an open api (application programming interface), multi-domain simulation framework across different industries, Accellera Systems Initiative, has announced a Federated Simulation Standard proposed working group. Its first meeting to “gather input and discuss expectations” will be held in Toulouse, France on 25 and 26 September. Different industries, for example avionics, space, semiconductor, automotive and ...

Intel and Synopsys to build IP portfolio for 3nm & 18A

Intel and Synopsys are to develop IP on Intel 3 and Intel 18A for Intel’s foundry customers. The availability of IP on Intel advanced process nodes is intended to create a more robust offering for IFS customers. As part of the transaction, Synopsys will enable a range of its standardised interface IP portfolio on Intel’s process technologies. As a result, ...

AI accelerates design automation

Design tools made room for AI at this year’s DAC, as electronic design automation companies integrate the technology to automation, analyse and accelerate designs, reports Caroline Hayes. Siemens Digital Industries software tied two themes of the Design Automation Conference (DAC) together in one new product when it announced Solido Design Environment, an artificial intelligence (AI) -powered IC design and verification ...

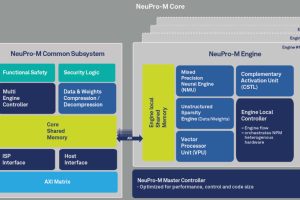

Ceva adds cores and generative AI to neural processing IP portfolio

Ceva has filled-out its NeuPro-M family of neural processing units, and boosted its architecture for generative AI algorithms. “NeuPro-M NPU architecture and tools have been redesigned to support transformer networks in addition to convolutional neural networks,” according to the company. “This enables applications leveraging the capabilities of generative and classic AI to be developed and run on the NeuPro-M NPU.” ...

Viewpoint: Peace breaks out in robotic patents war?

The robotic patents war is not over but disputes don’t have to reach court, writes Alexander Ford of Withers & Rogers, in the wake of the Ocado and AutoStore settlement. Following a three-year-long legal dispute over alleged patent infringement, Ocado and Norwegian robotic tech company, AutoStore, have reached an out-of-court settlement. But the robot patent war is far from being ...

MEMS accelerometer signal chain modelling in LTSpice

Dmitry Vasilenko, of Arrow Electronics, provides some design hints to accelerate the mechanical model of an accelerometer. Micro-mechanical systems (MEMS) have become common. They are used for acceleration measurement in a multitude of designs, from in-vehicle systems to fitness trackers. Figure 1 shows the operation principle of an accelerometer. The basis of such a sensor is a movable proof mass ...

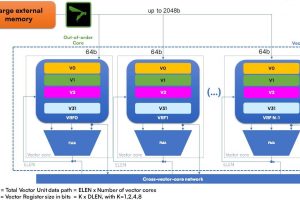

RISC-V Summit: Customisable vector unit

Semidynamics has announced a customisable vector unit for RISC-V processor cores, compliant with RISC-V vector specification 1.0. Vector unit are composed of several vector cores that perform multiple calculations in parallel. In this case, Semidynamics’ vector core can be tailored to support FP64, FP32, FP16, BF16, INT64, INT32, INT16 or INT8 data types depending on requirements – the longest word-length ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News