At Embedded World this morning, RISC-V International announced approval of its E-Trace (Efficient Trace for Risc-V) and SBI (RISC-V supervisor binary interface) specifications. E-Trace defines an approach to processor tracing that uses a branch trace, intended for debugging any size of application up to super computers. The documentation specifies the signals between the RISC-V core and the encoder (or ingress ...

EDA and IP

SkyWater adds FDSOI SRAM IP

Skywater, the US hi-rel foundry, has added FDSOI SRAM on 90nm to its IP portfolio. Mobile Semiconductor will provide two SRAM compilers for SkyWater customers developing products on its RH90 platform. This is the latest step in SkyWater’s RH90 technology roadmap. The company has leveraged the $170 million investment by the Department of Defense (DOD) to broaden onshore production capabilities ...

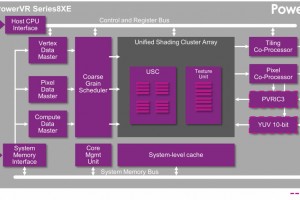

Imagination offers licence-free GPU and AI accelerator IP to early-stage companies

Imagination Technologies is offering early-stage companies access to IP for four of its PowerVR Series8XE GPUs and three Series3NX neural network accelerators without any licensing costs. “This lowers the barriers of entry to SoC design, enabling scale-ups to create IoT and AI products for applications covering smart home, industrial designs for smart cities or smart factories, smart kiosks and signage ...

Siemens Digital brings out Nucleus ReadyStart

Siemens Digital Industries Software announced today availability of its leading Nucleus ReadyStart solution for embedded development targeting the fast-growing adoption of the RISC-V architecture. Building on one of the industry’s first commercial real-time operating systems (RTOSes) for RISC-V devices, released in 2021, Siemens’ newest Nucleus ReadyStart embedded development solution includes a host of new features that help customers enhance the ...

The biggest challenge for AI is to make it easy to use

The industry and many markets have embraced big data analytics but this will mean a re-think for chip designers who will need new tools to create competitive solutions. According to Ravi Subramanian, senior vice president and general manager of IC verification solutions, Siemens EDA. AI and software are pushing sensing and electronics to the network edge in order to provide ...

UK GaN micro-LED display at San Jose Display Week

Cambridge GaN colour micro-LED company Porotech will be unveiling a multi-colour display technology at Display Week in California next week, using identical pixels from a single wafer to create colour. Its “PoroGaN platform makes it possible for each individual tiny LED on an epiwafer to emit all colours of the visible spectrum”, according to the company. “At this stage, the proof-of-concept displays ...

Sponsored Content: Cybersecurity with Tessent Embedded Analytics

There’s a strong case for using hardware-based threat detection and mitigation. SoC design teams fill a mission-critical role in ensuring cyber-physical safety and security for electrical and electronic systems that are connected to the internet. The requirements and tools available to achieve this goal are ever-shifting, but we can be fairly sure that traditional software-only security measures are unlikely to ...

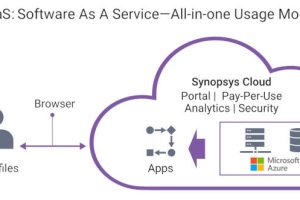

Synopsys launches pay-as-you-go chip design and verification tools on Azure

Synopsys has picked Microsoft’s Azure HBv3 cloud to offer pay-as-you-go on-line IC design and verification electronic design automation (EDA) tools, to be called Synopsys Cloud. “As more design flows incorporate AI, requiring even more resources, the virtually unlimited compute and EDA access we’re providing will deliver a flexible, secure chip development environment for future demands,” said Synopsys CEO Sassine Ghazi. “Synopsys Cloud ...

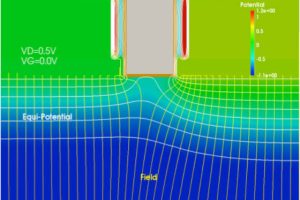

Glasgow transistor improves margins in DRAM

“More than 50% reduction of the statistical variability compared to bulk mosfets with identical dimensions”, is the claim of Glasgow-based Semiwise for its ‘flat field transistor’, which “is complemented by 30% performance increase and 5% reduction of the manufacturing costs compared to the equivalent bulk CMOS technology transistors.” The company is aiming its flat field transistor (right) at the sense ...

MathWorks updates MATLAB and Simulink

MathWorks has released 2022a of the MATLAB and Simulink product families. Release 2022a (R2022a) offers hundreds of new and updated features and functions in MATLAB and Simulink along with five new products and 11 major updates. New capabilities in MATLAB include new apps and App Designer functions, graphics enhancements, and the ability to customize Live Editor tasks. Simulink updates enable users to streamline masking workflows with ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News