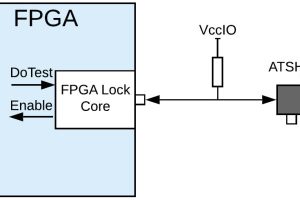

Protecting against IP theft, and to prevent contract manufacture hardware counterfeiting, ‘FPGA Lock’ from Nial Stewart Developments is an intellectual property block for FPGAs that communicates with Microchip’s SOT-23 ATSHA204A crypo-authentication IC. The cores uses generic Intel altsyncram and Xilinx 7 series blockram macros and occupies ~720 registers and two ram blocks. Only one pin on the FPGA is needed, ...

EDA and IP

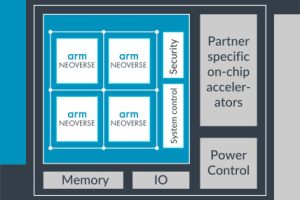

Faraday Technology plans 64 core ARM design on Intel 18A process

Taiwanese SoC design house Faraday Technology is collaborating with Arm and Intel on a 64-core system-on-chip, intended to be made with Arm Neoverse data-centre-grade cores using Intel’s 18A (nominally 1.8nm) foundry process – the latter due to become available at the end of this year. It will use Arm Neoverse Compute Subsystems (CSS, pictured), where “Arm delivers validated, performance-optimised compute ...

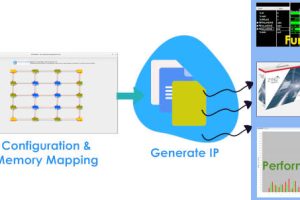

Try a network-on-chip configuration tool?

SignatureIP is offering a trial of its processor agnostic network-on-chip (NoC) configuration software. Called iNoCulator, the “tool enables users to find the optimal NoC configuration, and the company believes that it is the fastest on the market”, it said. “This try-before-you-buy offer will enable engineers to see for themselves just how easy it is to design a NoC with our tool.” ...

Cadence adds apps for billion gate SoCs to emulation hardware

Cadence has added three apps to its Palladium Z2 emulation hardware for SoCs. “These domain-specific apps allow customers to manage increasing system design complexity, improving system-level accuracy and accelerating low-power verification for applications such as artificial intelligence, machine learning, hyperscale and mobile,” according to the company. They are: Four-state emulation for simulations requiring X-propagation, such as for low-power verification of ...

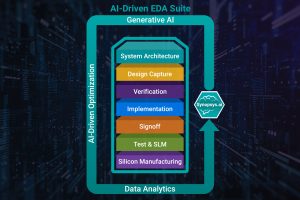

Synopsys extends GenAi across full stack

Synopsys is expanding its Synopsys.ai EDA suite to bring GenAI across the full stack to improve engineering productivity for the semiconductor industry. This expands upon Synopsys’ recent announcement to deliver Synopsys.ai Copilot, the first in a series of GenAI capabilities for chip design. Early collaborations with AMD, Intel, and Microsoft have substantiated the power of generative AI for chip design. ...

Viewpoint: Patent dispute – Amazon, Nokia clash over video streaming

Amazon may be in a tight spot in its video streaming technology dispute with Nokia, but there are options, writes John-Paul Rooney, a consumer tech specialist at European intellectual property firm Withers & Rogers. News that tech innovator Nokia is suing Amazon in five jurisdictions – the UK, Germany, India, the European Unified Patent Court, and the US – for ...

Synopsys and Microsoft deploy AI to design ICs

Synopsys and Microsoft have developed Synopsys.ai Copilot which designs ICs for the Azure Open AI Service. Synopsys.ai is an AI-driven EDA suite. Azure OpenAI Service gives access to OpenAI’s large language models (LLMs) with the enterprise-ready capabilities of Microsoft Azure. Together, the companies collaborated to support Synopsys’ development of Synopsys.ai Copilot, bringing together Azure OpenAI Service generative AI capabilities with ...

Cadence offers academia PDK for open source 130nm SkyWater process

A PDK for the SkyWater open-source 130 nm process will be available in the Cadence VLSI (very large-scale integration) Fundamentals Education Kit. The kit teaches students how theories and concepts can be applied in the design of simple logic circuits and in the physical implementation of a simplified microprocessor. SkyWater collaborated with Cadence to create an open-source chip manufacturing program ...

SiTime buys Aura Semi’s clock products and licenses Aura’s clock IP

SiTime is to acquire the clock products of Aura Semiconductor and license all of its clock IP in an all-cash transaction, comprised of fixed payments totaling $148 million, and earnouts capped at $120 million. “SiTime’s vision is to transform all categories of the $10 billion timing market,” said Rajesh Vashist, CEO and chairman of SiTime, “since our IPO in 2019, ...

Fraunhofer IESE partners for AI chip network-on-chip architecture

Faster on-die memory access for AI processing could spring from a collaboration between network-on-chip intellectual property company Arteris and the Fraunhofer Institute for Experimental Software Engineering (Fraunhofer IESE). Memory access is important with neural network algorithms as their execution requires large quantities of data to be transferred between processing elements and memory, increasing emphasis on the performance of the access ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News