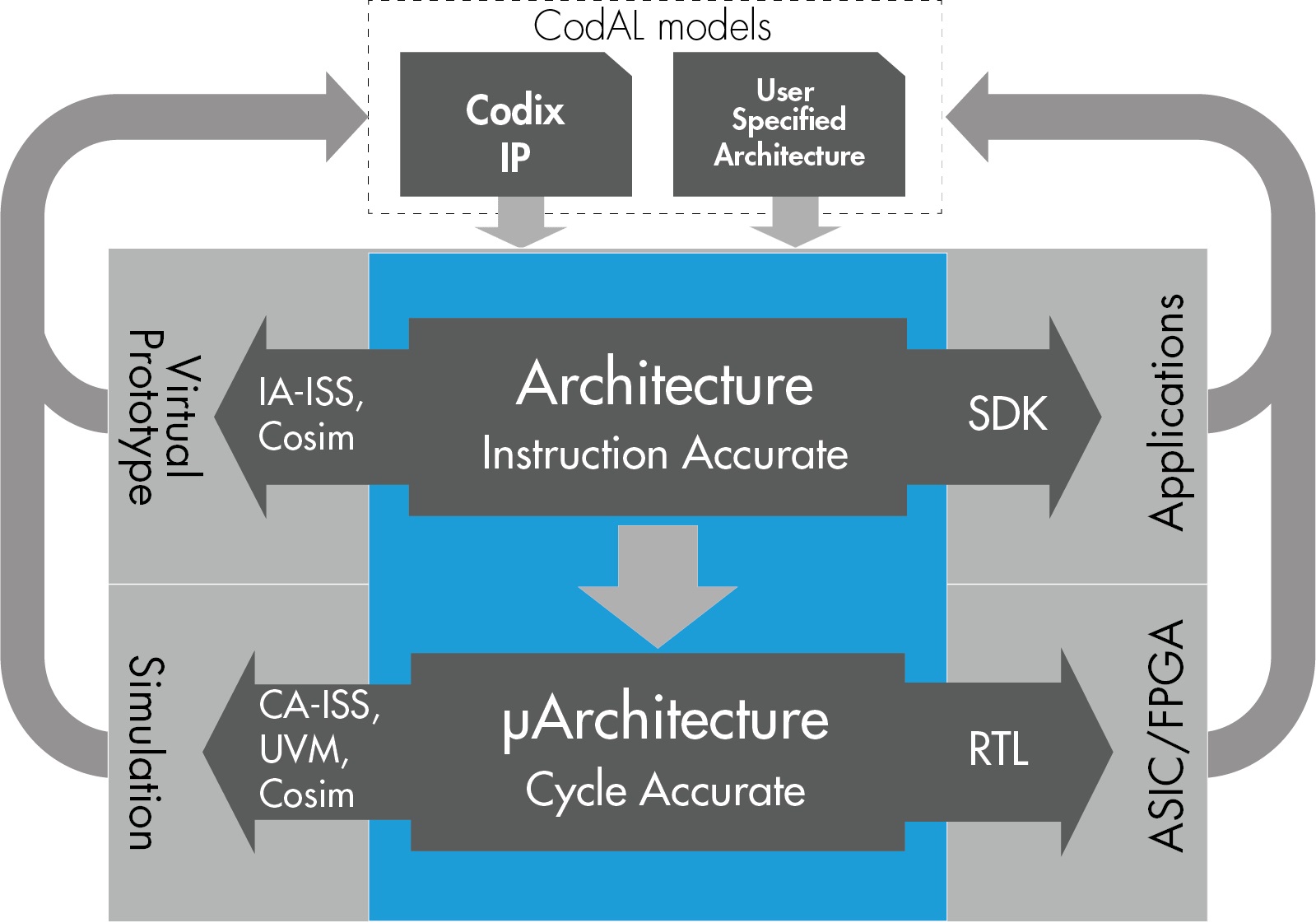

System designers can use the Codasip Studio toolchain to find the best software and hardware trade-offs and achieve optimal features and PPA (Power, Performance, Area).

The combination of customisable processors and tools for processor design enables an automated approach to achieve Custom Compute. To make this customisation usable for software developers, Codasip makes sure that all tools—including the compiler and debugger—also support customisation.

approach to achieve Custom Compute. To make this customisation usable for software developers, Codasip makes sure that all tools—including the compiler and debugger—also support customisation.

This now includes the trace solution.Including trace in an SoC significantly speeds up the time-consuming software debug task and hereby reduces the bring-up time and the cost of software development.

The Tessent Enhanced Trace Encoder builds on the RISC-V standard produced by the Debug and Trace Working Group, which was led by representatives from Siemens who donated the Trace algorithm to the RISC-V International community.

However, the solution from Siemens goes well beyond the RISC-V standard, offering a tool with productivity gains in the development of the most complex systems, and it supports custom instructions.

It conducts detailed examinations on systems to find the bug and its root cause. It is cycle-accurate, which means the developer gets insights into each and every instruction.Mike Eftimakis, VP Strategy and Ecosystem, Codasip, commented,

“We wanted a trace solution that went much further than the RISC-V standard,” says Codasip vp Ankur Gupta, “Tessent Embedded Analytics enables system-wide real-time debug and post-deployment analytics, helping SoC providers focus on the key task of producing high-quality, innovative products, and getting them to market quickly.”

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News