Running on Wednesday 23 February, at 2 p.m. CST, it will be presented by Dr. Sarah Harris, associate professor of electrical and computer engineering at the University of Nevada, Las Vegas.

Running on Wednesday 23 February, at 2 p.m. CST, it will be presented by Dr. Sarah Harris, associate professor of electrical and computer engineering at the University of Nevada, Las Vegas.

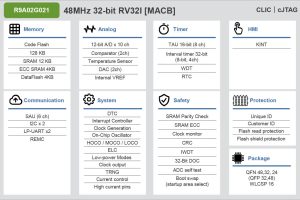

Specifically, the webinar will consider the inner workings of the RISC-V processor core and ways to implement a soft RISC-V processor core in a target (Xilinx) FPGA device.

Including, how to target a commercial RISC-V core (SweRV EH1) and system-on-chip (SoC) to an FPGA, how to program the RISC-V SoC and add more functionality to the RISC-V SoC, and how to analyze and modify the RISC-V core and memory hierarchy.

“RISC-V is open-source and royalty-free, and I am excited to share how this relatively new computer technology is enabling a new era of processor innovation on this RVfpga webinar,” said Dr. Harris. “I’m looking forward to seeing what new innovations engineers and makers can design with this more accessible open architecture option.”

You can register for the webinar here.

“We are pleased to present this RVfpga webinar as it will be a great resource on the topic of RISC-V for our customers and community,” said Y.C. Wang, director, global academic program for Digi-Key. “This presentation will help the next generation of programmers and engineers better understand how to utilize and experiment with the rich plethora of RISC-V products we have in stock.”

RISC-V resources on the Digi-Key website can be found here.

See also: RISC-V reviews progress

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News