SiFive has announced a quad-core RISC-V development board. HiFive Premier P550, as it will be known, is built around an Eswin EIC7700 processor which has SiFive’s 64bit three-issue, out-of-order P550 cores, 256kbyte L2 cache and 4Mbyte L3 cache. It is collaborating with Canonical to ensure Ubuntu will run on the board, which is similar to a PC motherboard. “The board ...

Tag Archives: RISC-V

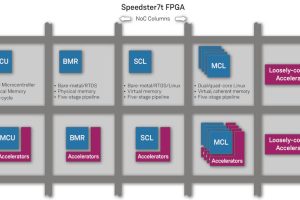

Linux-capable RISC-V soft cores for Achronix FPGAs

Achronix has teamed up with Bluespec to offer a family of Linux-capable RISC-V soft processors for the Speedster7t FPGA family. “Bluespec’s RISC-V processors now integrate into the Achronix 2D network-on-chip architecture, simplifying integration and enabling engineers to add scalable processing to their designs,” according to Achronix. “The network allows multiple instances of the RISC-V core to be added, and relocated ...

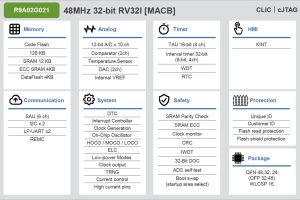

Renesas dips toes into few-pin RISC-V MCUs

Resasas has put its in-house developed 32bit RISC-V core into a few-pin general-purpose MCU series, following earlier RISC-V projects with Anders and SiFive. Announced last November, the core implementation can accommodate various standard RISC-V options, to which Renesas has added its own options including: a stack monitor register to protect against rogue software, a dynamic branch prediction unit improve the ...

Ecosystems and equality, the route to Risc-V

Calista Redmond is passionate about securing a strong hardware and software ecosystem for the open instruction set architecture and technology’s role in creating positive change. Interview by Caroline Hayes. Risc-V International promotes adoption of the open standard instruction set and an ecosystem of hardware and software. Calista says the momentum is international, with a strong balance of Risc-V development and ...

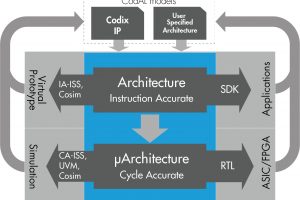

Codasip adds family of RISC-V processors for custom compute

Codasip, the RISC-V custom compute specialist, has brought out a configurable family of RISC-V baseline processors. The 700 family includes application and embedded cores. Customers can use Codasip Studio to optimise each baseline core for their target use case. The first core in the family is A730, a 64-bit RISC-V application core that is now provided to early-access customers. “By ...

Qualcomm and Google to develop RISC-V for wearables

Qualcomm is to create RISC-V based silicon for wearables, working with Google to optimise it for Google’s Wear OS. “We are excited to extend our work with Qualcomm Technologies and bring a RISC-V wearable solution to market,” said Google general manager Bjorn Kilburn. Leading up to this, the companies will continue to invest in Snapdragon Wear platforms for the Wear ...

Most Read articles – RISC-V, Nvidia Orin, O-RAN radio

There's O-RAN reference designs, four channel 12bit oscilloscopes, a rugged waterproof camera, Graphcore losses and the U.S. stance on RISC-V and China...

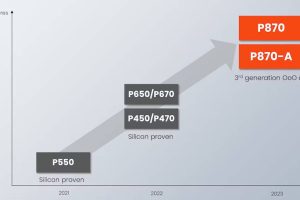

SiFive’s high-performance RISC-Vs for AI and machine learning

SiFive has announced a pair of high-end RISC-V cores for AI and machine learning in consumer, automotive and infrastructure markets. “Performance P870 and Intelligence X390 offer a new level of low power compute density and vector compute capability, and when combined provide performance for data intensive compute,” according to the company, which is advocating combining the general-purpose scalar P870 with ...

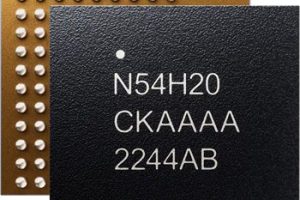

Nordic combines Arm and RISC-V for ‘remarkable’ EEMBC benchmarks

Nordic Semiconductor has announced EEMBC benchmarks for its forthcoming multi-protocol nRF54H20 wireless microcontroller, which combines multiple Arm Cortex-M33 processors and multiple RISC-V coprocessors “optimised for specific types of workloads”, it said, adding that developers will be able to dynamically change between configurations for processing ability or energy efficiency. Configured for high processing efficiency, it got a ULPMark-CM score of 170 ...

Codasip offers Siemens’ Tessent Enhance Trace Encoder

Codasip, RISC-V Custom Compute specialist, now offers Siemens EDA’s Tessent Enhanced Trace Encoder product with its customisable RISC-V cores, allowing developers to trace and debug issues between silicon and software, and understand real-time behaviour of designs based on Codasip processors System designers can use the Codasip Studio toolchain to find the best software and hardware trade-offs and achieve optimal features ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News