The device contains 1,270 logic elements, typically equivalent to 980 macrocells, said the firm, and 8kbit of memory. It has up to 212 user I/O pins and a worst case tPD (pin to pin delay) of 6.1ns.

Three speed grades are available. The -3 has a 304MHz maximum clock frequency for a 16-bit counter, 154MHz for a 64-bit counter. The -5 runs the two test circuits at 215MHz and 96MHz.

User flash memory and configuration memory are specified for a minimum of 100 program/erase cycles. Power-up time is 200µs.

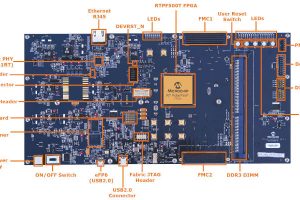

A low-cost development kit featuring the EPM1270 will be available for purchase from distributors early in the fourth quarter of 2004 for $150. The development kit includes a PCI form factor PCB with a 32-bit edge connector, programming and USB cables, several demonstration designs, Quartus II Web Edition development software and complete documentation.

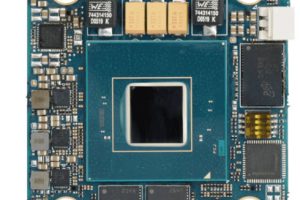

The MAX II device family includes four members ranging in density from 240 to 2,210 logic elements (LEs). Package options include a 17x17mm 1.0-mm FineLine BGA (212 I/Os) and 22x22mm 0.5-mm thin quad flat pack (116 I/Os).

The EPM1270 is priced at $4.25 in high volume (500,000 units).

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News