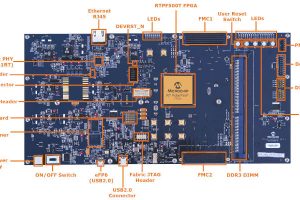

Design tool firm Altium’s latest JTAG interface is intended to allow system developers to use the firm’s Nexar test tool with their existing FPGA development boards to interactively design and debug digital systems, including entire processor-based systems on an FPGA in a more cost effective manner.

According to the firm it removes the need to make a special development board purchase.

The universal JTAG interface attaches to the parallel port of a developer’s computer and features a set of flying leads that connect to the target development board. The interface supports two independent JTAG connections. One to the JTAG programming pins of the target FPGA and the other to four general I/O pins of the FPGA used to establish a secondary ‘soft’ JTAG chain inside the device.

The interface supports both the Xilinx ISE and Altera ByteBlaster cable standards.

Email: info.de@altium.com

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News