AccelChip is offering fixed-point linear algebra intellectual property (IP) as stand-alone RTL cores.

As part of the firm’s AccelCore product line the FPGA and Asic cores include matrix inverse and factorisation cores used in applications such as beam-forming, software-defined radio, radar/sonar, Kalman filtering, and other wireless applications.

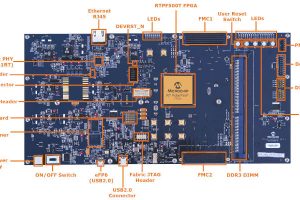

The pre-verified VHDL/Verilog cores have been fully synthesised and validated on Xilinx and Altera FPGAs.

Typically performing matrix factorisation and inversion in hardware has been difficult because the algorithms are complex and sensitive to numerical problems, particularly when using fixed-point arithmetic commonly used in devices. As a result, designers usually implement these linear algebra algorithms in C on DSP or general-purpose processors.

The first release of AccelCore IP cores performs matrix inversion and factorisation using two methods – triangular-orthogonal factorization, or QR factorisation, as well as Cholesky factorization.

Evaluation copies of each IP core are available.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News