These cores can be used for building systems requiring very high throughput-rate standard Ethernet connections, including chip-to-optical module, chip-to-chip, and backplane applications.

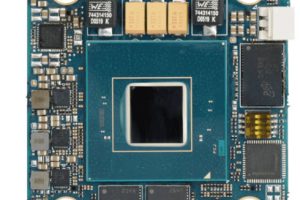

The media access control (MAC) and physical coding sublayer plus physical media attachment (PCS+PMA) sublayer IP cores are IEEE 802.3ba-2010 standard compliant, reducing design complexity for customers integrating 40GbE and 100GbE connections on Altera’s 28-nm Stratix V FPGAs and 40-nm Stratix IV FPGAs.

“As more system designs use Ethernet at high speeds—not only for local-area network attachment but to interconnect within systems—subsystem IP, including 40GbE/100GbE MAC and PCS+PMA layers, becomes a vital component in the system design team’s toolkit,” said Vince Hu, v-p product marketing at Altera.

The 40GbE and 100GbE MAC and PHY IP cores provide an interface composed of a single packet-based channel that is logically compatible with previous-generation Ethernet systems.

The cores are supported in Altera’s Stratix V GT and GX FPGAs with transceivers operating at data rates up to 28.05Gbit/s and 14.1Gbit/s, respectively, and Stratix IV GT FPGAs with transceivers operating at data rates up to 11.3Gbit/s.

Stratix FPGAs combine high density, high performance and a rich feature set, allowing customers to integrate more functions and maximize system bandwidth.

Altera’s 40GbE and 100GbE IP cores are available for separate download from Altera.com and are compatible with the recently announced Quartus II software v12.0.

For more information on Altera’s 40GbE and 100GbE IP cores, please visit www.altera.com/40-100GbE. For pricing information, please contact sales@altera.com.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News