Designers can used the integrated development environment (IDE) to quickly go from C++ to FPGA using the HLS and Achronix’s ACE design tools. The combination can reduce the development effort for 5G wireless and other design applications that require high performance FPGA technology in SoCs, configured using a proven C‑based design flow.

Ellie Burns, director of marketing, Calypto Systems division, Mentor said: “Achronix eFPGA offers a tremendous ability to adapt to late changing and new requirements in a field programmable SoC. Coupled with Catapult HLS and the verification speed of C++, chip designers can now easily go from algorithm change to new low-power, high-performance hardware in days rather than weeks or months.”

The partners’ technology flow allows designers to make algorithmic changes in the late stages of IP development and to optimise the digital micro-architecture. Software tests for generated register transfer level (RTL) code can be reused, which is claimed to reduce the need for dedicated RTL test benches by over 80%.

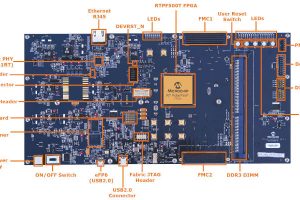

Speedcore eFPGA IP enables customers to create a customised programmable fabric, with specific logic, memory and DSP resources to meet a particular application’s requirements. As well as the 5G wireless infrastructure, they can be used in data centres, advanced driver assistance systems (ADAS) and autonomous vehicles.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News