Certus-NX FPGAs, as they will be known, are intended to be general purpose, aimed at applications from data processing in automated industrial equipment to system management in communications infrastructure, said the company.

“Technology trends like industrial automation and 5G have developers looking to add processing and connectivity to applications that operate at the network Edge,” said Lattice. “To support these trends, devices require low power processing hardware with support for popular interfaces like PCIe and Gigabit Ethernet.

“Technology trends like industrial automation and 5G have developers looking to add processing and connectivity to applications that operate at the network Edge,” said Lattice. “To support these trends, devices require low power processing hardware with support for popular interfaces like PCIe and Gigabit Ethernet.

So what are the features?

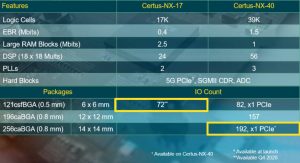

- Small form – “Certus-NX FPGAs can enable a complete PCIe solution with a size of 36mm2“, said Lattice.

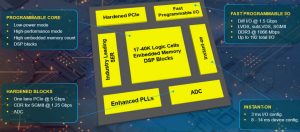

- IP blocks including:

1.5 Gbit/s differential I/O

5 Gbit/s PCIe

1.5 Gbit/s SGMII

1,066Mbit/s DDR3 - AES-256 encryption support and ECDSA authentication to secure the devices’ bit stream against unauthorised access, alteration or copying.

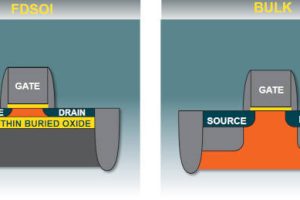

- Programmable FDSoI back-bias for user-selectable performance/power trading

- Fast start – individual I/Os configured in 3ms, full start in 8-14ms depending on device capacity

- Good soft-error rate (SER) through FDSoI construction. ECC and SEC supported in hardware.

Selected customers already have samples.

For software development, Lattice provides its Radiant FPGA design environment, which was stepped up to version 2.1 to accommodate Certus-NX.

The new version of Radiant supports SystemVerilog throughout the design flow, from the native synthesis tool through the schematic viewer, hierarchical viewer, configuration wizards, and debugging tool.

“Many FPGA designers are moving to design solutions that leverage SystemVerilog as it gives them more coding efficiency and granular control over their application at every step in the design flow,” said Lattice product manager Roger Do.

Radiant’s drag-and-drop GUI as seen some attention, with a redesigned to support an I/O planner that enforces correct pin placement for each I/O signal or bus.

Radiant also supports the CrossLink-NX FPGAs for embedded and smart visions applications, as well as the lower power, smaller form iCE40 UltraPlus FPGAs.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News