There was a lot of activity around RISC-V, including a presentation by Imperas Software (www.imperas.com) entitled What’s Next for RISC-V? Vectors, Verification, and Value-added Extensions. During the event, the company announced that its RISC-V reference models have been implemented by the OpenHW Group to establish the Core-V processor verification test bench which will validate open source cores for the open source community.

Explaining the alliance’s aim for best practices for hardware and software designers to collaboratively develop open source cores, IP, tools and software, founder and CEO, Rick O’Connor said “The OpenHW Verification Task Group developed and published a [design verification] test plan and implemented an open engineering-in-progress approach as we complete the verification tasks using the Imperas golden RISC-V reference model.”

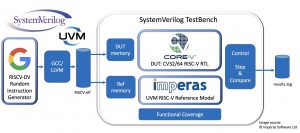

“Simulation is central to the entire semiconductor design and verification flow, and while a processor is described in Verilog RTL, the industry standard for test benches is SystemVerilog,” said Steve Richmond, verification manager at Silicon Laboratories and co-chair of the OpenHW Group Verification Task Group. The group used the RISC-V golden model within the universal verification methodology (UVM) SystemVerilog methodologies for processor verification and, in the case of any issues, support analysis and resolution.

To support the verification work, Imperas has developed a SystemVerilog testbench framework which is maintained as part of the OVPworld.org library of example platforms. The library of processor models and example platforms, together with the OVP golden reference model and example step and compare testbench can be found at www.OVPworld.org.

The OpenHW Group Core-V Design Verification (DV) test plan is available here and the UVM testbench GitHub repository here.

Modular RISC-V customisation

For embedded Linux applications, Codasip unveiled its Bk7 core, a member of its RISC-V processor IP family. It can be used to customise applications which require embedded Linux, such as security and real time AI.

The 64-bit processor core has a single in-order seven-stage pipeline, which complies with the RV64IMAFDC instruction set architecture (ISA). The open RISC-V standard offers an advantage over general purpose processor architectures in that the core can be configured and extended to fit domain-specific needs.

It is designed to be “the fastest and most customisation-friendly design yet,” said notes Karel Masařík, CEO of Codasip. It does this by automating custom changes in the RTL code, the instruction set simulator and the compiler using the Studio toolset. The design tools use a single high-level description of a core written in CodAL, a C-like language. When the description is updated with the custom changes, Studio automatically generates customised hardware and software development kits, including a UVM (universal verification methodology) environment to deploy the core.

The company has enhanced CodAL to be used with modular design so that customizing the description is the only non-automated step, added CTO, Zdeněk Přikryl.

The off-the-shelf configuration of the processor includes support for the RISC-V atomic and floating point extensions (both single and double precision), a memory management unit and support for privilege modes, including Linux. There is also an internal interrupt controller, dynamic branch prediction and standard bus interfaces. Customisable options include the branch predictor, instruction and data caches and store buffer.

At the release, to coincide with DAC, the company said future releases will include tightly coupled memories, dual issue microarchitecture, and multi-core support.

The Bk7 package contains the CodAL description (fully editable in Codasip Studio), RTL code of the default configuration, the CodeSpace IDE to write software for the core, C compiler (LLVM and GCC), source files and compilation guide for Linux, and Linux boot demo SoC to deploy the core.

Codasip and Aldec co-hosted a presentation at DAC, entitled Integrated UVM Simulation Environment for Verifying Custom Instructions with RISC-V Cores.

For FPGA and asic designs, the latter has added Alint-Pro 2020.07, a RISC-V focused static verification rule set to Alint-Pro to statically validate HDL code quality prior to simulation. The rule set helps designers statically verify RISC-V designs and IP integrators to select and integrate open-source RISC-V cores into SoCs.

It verifies the correct use of constants and variables, port definitions, instantiations, and object references and verifies correct Verilog and SystemVerilog data types usage in expressions. Coding for implementation contains important code checks for optimal synthesis, timing closure and finite state machine implementation.

The SystemVerilog constructs set ensures optimal SystemVerilog usage for the RTL coding. It applies checks on instantiations and interfaces on SystemVerilog types and procedural blocks.

DSP design

Two announcements from eFPGA company, Menta, centred around its Origami tool suite. The company announced the latest release of its programming software, Origami Programmer 2020.1 and also introduced its Adaptive Digital Signal Processor (DSP) which can be inferred automatically using the Origami toolsuite within the user’s embedded FPGA (eFPGA).

Menta’s managing director, Yoan Dupret, explained that the Adaptive DSP allows the eFPGA IP to adapt to specific requirements. Users will be able to implement the ideal DSP architecture within the eFPGA IP that better suits the hardware requirement, says the company. Operand size can be chosen for both the multiplier and the arithmetic logic unit (ALU).

The DSP block operating modes are programmable through the bitstream, and can be dynamically reconfigured and its behaviour can be controlled at clock cycle level.

A finite impulse response (FIR) generator allows users to generate RTL code of an optimised FIR using the company’s DSP FIR engine. Users can select from four to 512 taps to define the number of DSP to use within an architecture, the data bus and the ALU size to meet frequency, area and latency goals.

DSP can be configured using Origami Designer eFPGA IP software graphical interface and the adaptive DSP is automatically inferred by Origami Programmer synthesis.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News