OneSpin Solutions and Austemper Design Systems will both highlight tools for functional safety verification. Austemper will focus on mission-critical system development, with the KaleidoScope tool suite which supports analogue design for concurrent, mixed-signal fault propagation. The automated tool suite has safety analysis, synthesis and verification capabilities for certification-oriented applications. It is used for large scale automotive designs in ADAS and autonomous driving. The concurrent fault simulation includes simulations recommended by ISO 26262 to comply with ASIL requirements.

The company recently partnered with OneSpin Solutions to adopt a tool-supported methodology for functional safety applications, combining a design and verification flow, which will be demonstrated at the OneSpin booth. Hardware safety mechanisms are inserted into chip designs and OneSpin Solutions’ tools formally verify the hardware safety logic. Equivalence checking ensures that the inserted safety logic does not affect regular functionality and fault detection analysis verifies that safety mechanisms perform properly in the event of random errors.

OneSpin is also promoting its Tool Qualification kit, following verification by TÜV SÜD of its tool development processes. The initial kit is available for the company’s 360 EC-FPGA EDA tool, an automatic sequential equivalence check that prevents FPGA design flows from introducing implementation errors. The kit is certified to ISO 26262, IEC 61508 and EN 50128.

FPGA insights

Still with FPGA design, Plunify has collaborated with Xilinx to offer the Vivado design suite in the cloud, via the Plunify Cloud platform. Designers pay as little as 50c to compile a Vivado project on the Amazon Web Services (AWS) cloud, including licenses.

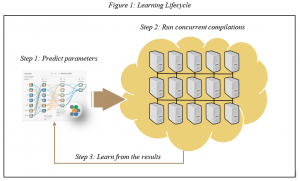

The company will also demonstrate enhancements to its InTime timing closure software to optimise FPGA timing in the cloud (Figure 1). InTime Optimization Methodology can improve clock frequency by 20 to 80% and meet timing requirements in days, rather than weeks via machine learning. The software also accelerates timing closure and optimisation and is accessed via the cloud.

The company will also demonstrate enhancements to its InTime timing closure software to optimise FPGA timing in the cloud (Figure 1). InTime Optimization Methodology can improve clock frequency by 20 to 80% and meet timing requirements in days, rather than weeks via machine learning. The software also accelerates timing closure and optimisation and is accessed via the cloud.

Promoting eFPGA technology, Achronix Semiconductor is collaborating with IP specialist CAST to increase throughput and make savings in memory storage.

The two exhibitors will explain how CAST’s lossless compression IP has been ported to the Achronix FPGA portfolio for use in data centre and mobile edge data transfer applications. The hardware implementation of the lossless compression standard for Deflate, GZIP and ZLIB, is compatible with software implementations used for compression or decompression to provide up to 100Gbit/s throughput with low compression and low latency, coupled with Speedcore eFPGA technology to move and store big data at a low power consumption.

Energy efficiency

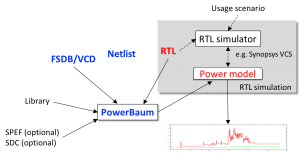

Speaking of power management, another exhibitor, Baum, identifies energy efficiency as the most under-developed area in chip design. Its automated power analysis and modelling tool is designed for automotive, IoT, mobile, networking and server projects. PowerBaum 2.0 (Figure 3) supports dynamic and static power, taking in RTL and netlist descriptions, and adds support for power analysis with hardware emulation. This, says the company, allows engineers to fix power bugs in realistic software scenarios. The tool also supports analysis with arbitrary temperatures which are specified by designers, to assess the effects of temperature on a design’s power consumption.

At DAC, the company will also introduce PowerWurzel, a gate level power analysis engine to be integrated with PowerBaum for power modelling.

Cloud-based SoC design and verification tools for IC design from Metrics include the Cloud Simulator and Verification Manager, designed to manage simulation requirements and resources, adjusting them up or down every minute. The company claims that Google Cloud enables unlimited UVM-compliant SystemVerilog simulation capacity and native, web-based verification management for faster regression times, reduced trunk code errors and predictable code coverage.

Aside from exhibitors, the event hosts technical sessions and a programme of keynotes addressing topical areas. This year, for example, Cadence will host a tutorial on ‘Functional Safety and Reliability for Automotive Applications’, and one on machine learning (‘Machine Learning Takes Speech Recognition Performance to the Next Level’). A keynote by Anna-Katrina Shedletsky, Instrumental, on Monday 25 June, will focus on ‘Automating Intelligence: Machine Learning and the Future of Manufacturing’. Using ML and AI for socially assistive robotics (SAR) is explored in Thursday’s keynote by Maja Matarić, University of Southern California who will present ‘Automation vs Augmentation: Socially Assistive Robotocs and the Future of Work’.

Another keynote advocates RISC-V as a means to free architects from proprietary instruction set architectures (ISAs). David A Patterson, Google and University of California, will present ‘A New Golden Age for Computer Architecture: Domain Specific Accelerators and Open RISC-V’.

A new area this year at DAC is the Design Infrastructure Alley. The initiative by the ESD Alliance and Association for High-Performance Computing Professionals is an area dedicated to the IT infrastructure for the design of electronic systems and components. As well as computing and storage requirements for design and managing use of the cloud, there is a dedicated Design-on-the-Cloud pavilion theatre discussing license management, grid computing and data security.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News