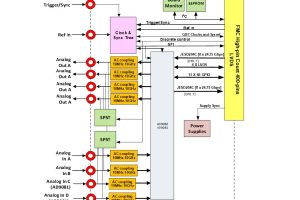

That is two channels of 12bit 2.6GHz instantaneous bandwidth, or one of 5.2GHz instantaneous bandwidth.

“The design comes from our centre in Friesing Germany – they have been designing high-speed ADCs there for for 20 years,” TI’s Paul McCormack told Electronics Weekly. “It is made on a 65nm pure CMOS process, not SiGe. The process has a good compromise between analogue and digital performance. The designers have become expert in getting the most out of this process.”

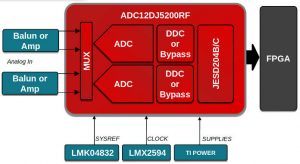

New to TI, the chip offers a JESD204C interface for connection to a host FPGA, which is more data-efficient than the earlier JESD204B interface – which is also offered by the chip. “JESD204C can save cost on the FPGA side as you can use an FPGA with fewer Gbit/s serdes [serialiser-deserialiser] lanes,” said McCormack.

16 or 8 lanes are available – up to 16 lanes at 10.4Gbit/s or up to 17.1Gbit/s over 8 lanes.

Full power analogue input bandwidth, at 8GHz (3dB 800mVp-p), is the widest in industry, according to TI, and the input is usable up to 10GHz.

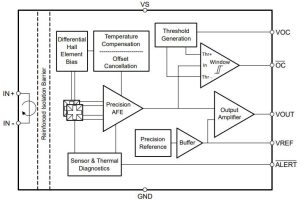

“The input is really good,” said McCormack, “it was a big part of the design. The input impedance is controlled at 100Ω differential, which is calibrated when switched on. For the first time in our ADCs, we have integrated a dither option which can be used to improve linearity or distortion performance in some applications.”

According to TI, it has the highest available dynamic performance across power-supply variations, even at minimum specifications, and can have an offset error as low as ±300µV, and zero temperature drift. Code error rate is claimed to be “more than 100 times better than competing devices”.

Power consumption is 4W, including the fast data interfaces, and it comes in a 10 x 10mm 144 ball BGA, which is pin-compatible with the slower ADC12DJ3200, ADC12DJ2700 or ADC08DJ3200.

Applications are expected in 5G testing, oscilloscopes and radar – the latter for direct X-band sampling.

It sounds well suited to software-defined radios, What about satellite use?

“We have made a 3.2Gsample/s ADC available for space,” said McCormack, “and we might do the same for the new part, it depends on demand.”

Tools

To test the ADC, evaluation boards ADC12DJ5200RFEVM and TSW14J57EVM are available, as is the ‘Multichip synchronisation reference design for clocking and power supply optimisation’.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News