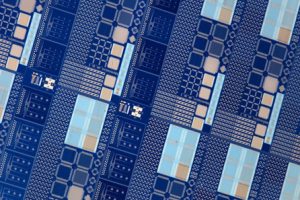

The development of silicon based semiconductor technology is heading towards increasingly smaller components: transistors are being scaled down to have nanometre dimensions. As an example, Intel are currently developing their 45nm and 64nm technologies, which are planned to take over from the current 90nm and 130nm processes used today in making most of their microprocessors.

Europe in general and the UK in particular is lagging behind the USA in this technology, and it is desirable that the European scientific and technological excellence in the field of silicon based nanodevice electronics is further strengthened.

|

| Dr Peter Wilson |

As feature sizes move to deep submicron (DSM) and designers need to squeeze more performance out and save more power, design tools and methods become vital for designers to achieve their requirements in a timely manner.

The UK still has a strong design base in the analogue IC industry, but is in danger of losing the capability to keep up with an under funded and shrinking research community. If the UK wishes to keep its analogue capability on the world level in the future it is essential that funding is forthcoming to support both research and teaching in leading UK universities.

This means proactive support for research projects, pressure on the funding councils and government agencies to provide specific resources for analogue IC design and commitment to supporting students at Masters and PhD level to ensure that there is a pipeline of high quality graduates coming to UK companies. Without such support, there is a serious danger of research in this area withering.

So, what are the key issues to be addressed? As device dimensions shrink due to ever-improving process technology digital circuitry continues to thrive.

The reality of multi-processors on a single die has been realized and the prospects for continued success, subject to proper power management, beyond 65nm technology are bright.

Due to this massive amount of integration capability, the need for greater amounts of supporting analogue and mixed-signal (AMS) circuitry on a mostly digital chip has grown. Integrating advanced power management, sensor interfaces, RF interfaces and signal processing blocks onto the chip has increased the complexity of the AMS technology on the chip.

Crucially this is becoming a serious design bottleneck. It is interesting to note that typically 10 per cent of the chip design may be analogue, but that this requires 90 per cent of the design time. Analogue supporting circuitry for these massive digital chips has been able to keep pace down to the 0.35µm (and perhaps even 0.18µm) technology node with successful design reuse and process migration. Even when the ever-important semiconductor device models for the MOS transistor have reached their limits of predictability.

However, continued physical scaling beneath 0.35µm means significant reduction in power supply voltage (i.e., from 3.3V to less than 1.5V). This means classical circuit topologies and approaches will no longer work. We need to be able to design effectively taking into consideration much greater process variations, higher susceptibility to supply voltage variations, thermal issues and designing for maximum yield.

There is currently a window of opportunity for UK researchers and the UK IC industry to work together, and by doing this have a fighting chance of remaining at the forefront of analogue IC design in the future by addressing some of these critical design challenges.

Dr Peter Wilson is from the School of Electronics & Computer Science, University of Southampton

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News