Choosing the most efficient test patterns and setting coverage targets have always been a challenge, and they become ever more daunting with the addition of new types of patterns. Design for test (DFT) teams can spend years establishing automatic test pattern generation (ATPG) targets – such as a coverage goal, pattern size, or some other metric – just for stuck-at and transition fault models.

Choosing the most efficient test patterns and setting coverage targets have always been a challenge, and they become ever more daunting with the addition of new types of patterns. Design for test (DFT) teams can spend years establishing automatic test pattern generation (ATPG) targets – such as a coverage goal, pattern size, or some other metric – just for stuck-at and transition fault models.

Targets need to be adjusted for a new technology node when new fault models are introduced. Questions often posed by designers include ‘How do companies decide what targets to set?’ and ‘Which patterns are best to apply for a new fault model?’

Using newer models can make setting fault model target metrics more complicated because the target could be completely different from the test coverage based on the full fault list. For example, targeting a test coverage for all potential bridge faults could be a huge list. It might be possible to achieve 99% detection of all bridge faults, but miss hundreds of the most likely bridges. It is more effective to choose the subset of bridges that is most likely to occur.

Test coverage

Measuring the test coverage as a percentage by dividing the detected number of faults or defects by the total number of faults or defects calculates the test coverage, but has no relation to the probability of occurrences of manufacturing defects for individual faults. This approach makes it hard to create an optimally ordered pattern set. It can also lead to overly-large test pattern sets, longer than necessary test time and lower confidence in the estimates of IC quality.

There is a way to measure pattern value that provides a consistent assessment of the value of patterns based on the likelihood of particular physical defects occurring. This is accomplished through the use of critical area.

Critical area weighted ATPG capability enables DFT engineers to determine the best mix of patterns targeting specific faults and which samples of patterns to experiment with.

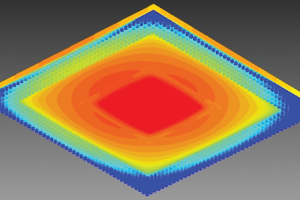

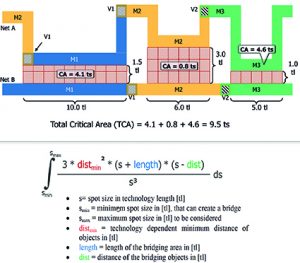

Critical area refers to the area in a design layout that determines the likelihood that a specific physical defect can cause a failure in the design (Figure 1). Total critical area (TCA) is the sum of all individual critical areas of a short between two connectors, or an open in a connection, weighted by the probability of occurrence of that spot size. It provides a common metric to assess a pattern’s impact on defects per million (DPM), which can be used to sort or order patterns to achieve the lowest DPM. The designer can therefore mix in patterns targeting new fault models for a more effective pattern set, even with the same number of patterns as the original pattern set. You can select or sort the most effective patterns from the entire pattern set based on their ability to detect physical defects.

Using TCA is a significantly better measure for the quality of the applied test patterns than counting just the number of faults or defects.

Pattern choices

TCA values are calculated using physical layout information. A user defined fault model (UDFM) file stores the models for each defect type (cell-internal, bridge, open, cell-neighbourhood). The UDFM files are input to the ATPG tool to generate test patterns and can be used to perform layout-aware and cell-aware failure diagnosis.

When read into the ATPG tool, the UDFM files containing TCA fault data can be applied to patterns to sort them from the highest TCA to the lowest.

Figure 2 shows how to load various fault models to optimise a pattern set. It can be used to simulate and calculate the TCA for an existing pattern set or to create a new pattern set from scratch. Reports can be generated to show the TCA included during ATPG, summary coverage, fault list and a layer-based TCA summary.

Some key elements of TCA-weighted ATPG include:

* Selecting the most effective patterns

* Choosing targets for pattern types and coverage

* Determining the effectiveness of new pattern types

* Grading pattern value by likelihood to detect defects

* Automatically sorting and selecting patterns

* Creating a smaller pattern set by targeting multiple fault models in our ATPG run.

TCA test pattern sets demonstrated equal or better defect detection with fewer patterns, which reduces test time and cost. TCA-weighted pattern selection represents a major step forward in ATPG for reducing test times for ICs, which require very low defectivity, including automotive ICs that need to meet the ISO 262622 functional safety and quality standard.

Critical facts

Tessent TestKompress is believed to be the first commercial automatic test pattern generation tool (ATPG) to use total critical area (TCA) calculation for all defects in the digital logic part of a chip.

Test coverage targets for static and dynamic patterns are usually based on the percentage of faults detected. These targets vary by company and it often takes years of production fail data to decide on appropriate goals. By the time a new fault model is needed, the target could be completely different than test coverage based on the full fault list.

Test coverage targets for static and dynamic patterns are usually based on the percentage of faults detected. These targets vary by company and it often takes years of production fail data to decide on appropriate goals. By the time a new fault model is needed, the target could be completely different than test coverage based on the full fault list.

Selecting patterns for production test is complicated by the inconsistent targets for various fault models. Patterns targeting stuck-at and transition faults traditionally target the number of faults detected. Bridge faults could be weighted based on parasitic capacitance, to create a smaller list than simply all potential bridges, but it would not be consistent with targets for other fault models. TCA provides a common metric for grading a pattern’s ability to detect defects.

All individual critical areas need to be taken into account to determine the likelihood of a specific physical defect occurring. Calculations have to include critical areas between connectors, as well as the probability of an occurrence. Rather than solely counting faults, TCA coverage takes the likelihood of defects into account and provides a consistent metric for all fault models.

Design for test engineers face challenges in setting target metrics for ATPG and choosing the best set of patterns for achieving high-quality test. Traditional coverage targets based on the number of faults detected do not consider the likelihood of one fault occurring compared to another. TCA ATPG technology enables the sorting and ordering of patterns based on their likelihood to detect defects. Users can create a pattern set for multiple fault models in one run, reducing the overall pattern size significantly.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News