The aim is to “reduce the effort required to integrate multiple analogue IPs into any asic by allowing the IP to be dropped straight into a digital design flow”, according to the company. “Crucially, customers no longer need to deal with the mixed-signal boundary between analogue and digital – the sub-systems look just like a normal block of digital IP, with the standard interfaces that engineers would expect, making them easy to understand and handle.”

Initially, the company is offering three sub-systems, for: power management (‘agilePMU’), process-voltage-temperature (PVT) sensing (‘agilePVT’), and sleep manangement (‘agileSMU’).

The IP blocks within a subsystem are from Agile’s existing portfolio and can be customised to customer requirements inside the digital wrapper, and it pre-verifies the mixed-signal sub-system so that the customer does not have to.

“The wrapped sub-systems are process and foundry agnostic, and each design is optimised for the customer’s specific PDK [process design kit],” said Agile.

Deliverables include SystemVerilog models for integration into customers’ existing digital verification flows.

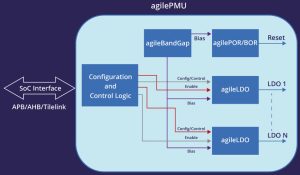

The power management sub-system (left) has power-on-reset, multiple programmable low drop-out regulators and a reference generator. It has a digital controller for control over start-up, supply sequencing and shut-down. Status monitoring provides real-time feedback.

The power management sub-system (left) has power-on-reset, multiple programmable low drop-out regulators and a reference generator. It has a digital controller for control over start-up, supply sequencing and shut-down. Status monitoring provides real-time feedback.

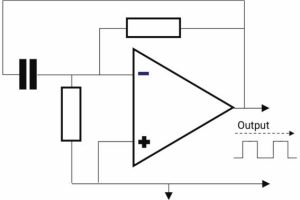

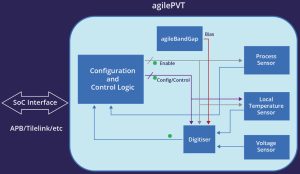

The PVT sensor (top) sub-system has process, voltage and temperature sensors, a reference generator and a digital controller for start-up and shut-down. Status monitors provide real-time feedback.

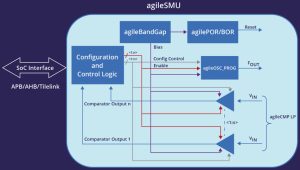

The sleep management sub-system (right) will typically contain a programmable oscillator for low frequency SoC operation and a number of comparators which can be used to initiate the wake-up sequence. A power-on-reset generator is included, as is a programmable RC-based oscillator. Activities are overseen by a digital controller, and status monitors provide real-time feedback.

Agile Analog is headquartered in Cambridge, UK.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News