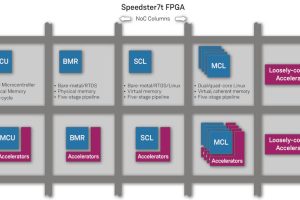

Achronix has teamed up with Bluespec to offer a family of Linux-capable RISC-V soft processors for the Speedster7t FPGA family. “Bluespec’s RISC-V processors now integrate into the Achronix 2D network-on-chip architecture, simplifying integration and enabling engineers to add scalable processing to their designs,” according to Achronix. “The network allows multiple instances of the RISC-V core to be added, and relocated ...

Tag Archives: fpga

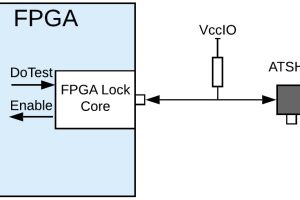

IP block secures FPGAs with one external IC

Protecting against IP theft, and to prevent contract manufacture hardware counterfeiting, ‘FPGA Lock’ from Nial Stewart Developments is an intellectual property block for FPGAs that communicates with Microchip’s SOT-23 ATSHA204A crypo-authentication IC. The cores uses generic Intel altsyncram and Xilinx 7 series blockram macros and occupies ~720 registers and two ram blocks. Only one pin on the FPGA is needed, ...

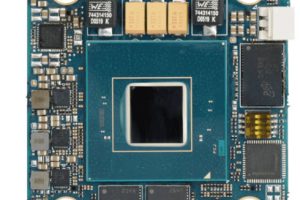

System-on-module built around Intel’s Agilex 5 E FPGAs

iWave has announced system-on-modules built around Intel’s Agilex 5 E-series FPGAs, which have AI algorithm support. iW-RainboW-G58M measures 60 x 70mm, and is available with any of the 5 E-series ICs that come in Intel’s B32A (32x32mm) package. “Agilex 5 system-on-module is an ideal building block for equipment used in wireless communications, video, broadcast and industrial test and measurement sectors,” ...

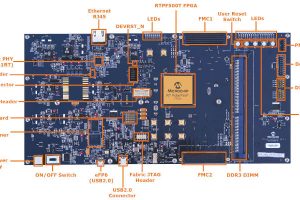

Dev kit for space-qualified FPGAs with QML qualification

Microchip is aiming at satellite designers with a development kit built around its radiation tolerant RT PolarFire FPGAs, for which MIL-STD-883 Class B qualification has been gained and both Class Q and Class V qualification have been sought. October 2023 update: RT PolarFire FPGA’s are now QML (qualified manufacturers list) Class Q qualified, as designated by the US Defense Logistics ...

Gadget Book: Getting Started with FPGAs

Here's a book you may consider worthy for your shelves. It's not strictly gadget-related, but FPGAs should be meat and drink for Electronics Weekly...

FPGAs for automotive lidar and cameras

AMD is aiming at automotive edge sensor fusion, for the likes of lidar, radar and 3D surround cameras, with a pair of FPGAs it has just started shipping. XA AU10P and XA AU15P are automotive-qualified, certified for functional safety up to ASIL-B, intended to be used in driver assistance systems, and come with the the company’s Artix UltraScale+ branding. The ...

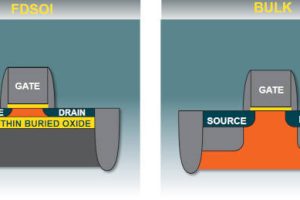

FD-SoI FPGAs get PCIe and LPDDR4 interfacing

Lattice Semiconductor is aiming at system control with a family of FPGAs that includes PCIe Gen 2 interfacing and embedded security. MachXO5T-NX, as they are called, are suited to “a set of control function designs for enterprise networking, machine vision and industrial IoT”, it said. They are built using the company’s FDSoI process (image right), which can dramatically reduce soft ...

Post-quantum cryptographic IP from Xiphera

Xiphera has announced intellectual property cores for implementing hardware post-quantum cryptography security on FPGAs and asics. Such security is executed on classical computing platforms to protect against quantum computing based attacks. Branded ‘xQlave’, the IP blocks are aimed at quantum-secure key exchange and digital signatures. “Powerful enough quantum computers will be able to break current public-key asymmetric cryptosystems based on ...

Functional safety certification for Microchip FPGAs

Microchip has created IEC 61508 Safety Integrity Level 3 functional safety certification packages for two of its FPGA containing IC ranges: SmartFusion 2 and Igloo 2. “Systems used in many high-reliability commercial aviation, space, defence, automotive and industrial applications require certification to the IEC 61508 SIL 3 functional safety specification,” according to the company. Package deliverables include certification of Microchip’s ...

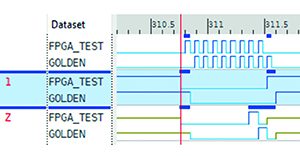

Verifying at a higher level of abstraction

Transaction-level modelling can help with certification-level verification if an FPGA application is safety-critical, says Krzysztof Szczur of Aldec. FPGA designs for avionics applications are increasingly employing high-speed interface buses to deliver greater performance and, if the application is safety-critical, verifying the design for certification purposes is challenging. Avionics buses use serial rather than parallel data transfer to reduce the number ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News