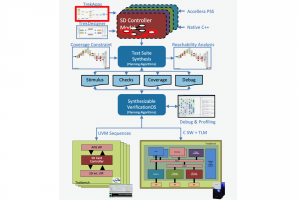

It offers parsers, analysers and elaborators for SystemVerilog IEEE 1800-2005 / 2009 / 2012 / 2017, VHDL IEEE 1076-1993 / 2002 / 2008 and UPF IEEE 1801-2009 / 2013 / 2015 / 2018. Full mixed SystemVerilog / VHDL language support is provided, together with a hierarchical technology-independent dabase, Verilog 2001, SystemVerilog test suites, with C++, Python and Perl APIs.

All platforms are distributed as C++ source code and compile on all 32-bit and 64-bit Linux, Mac and Windows OS. They can be used for formal verification, synthesis, simulation, emulation, virtual prototyping, in-circuit debug and design for test.

Using the parsers means that a company does not have to invest in an in-house HDL software team or spend time and money testing and debugging the HDL. Instead, says the company, it can concentrate on the core of an application to create differentiation and focus on the product design.

License models are royalty-free, and the source code means that users can control modifications, extensions, integration and compilation.

At DAC, the company highlighted the Invio layer which sits on top of the SystemVerilog, UPF and Liberty parsers. It has a set of APIs which can be directly referenced by connecting to objects at the HDL level to navigate designs and test benches. Its objects, such as instances, signals and processes, can be referenced by hierarchical names and all references (e.g. signals, classes, interfaces) are resolved for automatic support for complex SystemVerilog. The layer also supports user attributes and automatically enables a search on new user attributes.

In-place modification API allows the user to develop tools that modify existing RTL design but which features, such as indents, comments and white space, of the original text file.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News