Embench measures a processor’s performance using 19 real-world programs. The programs are deliberately selected from a range of authors and for a range of use-cases to match the breadth of modern embedded computing.

They’re run multiple times over the course of around 4 seconds to provide an accurate average runtime, and this data is provided both in its raw individual forms, and an overall geometric mean and standard deviation for the processor.

Additionally provided by the suite is the size of each program on the processor, representing the efficiency of the compiler used.

The reference platform is an Arm Cortex M4 using the GCC 9.2 compiler.

Conceived of by Prof David Patterson Emeritus Processor of Computer Science at UC Berkeley and Turing Award laureate, the suite was developed as a response to modern embedded computing requirements, which Patterson believed were not appropriately measured by traditional benchmark programs.

Embench vice chair Jeremy Bennett told EW the widely-used Coremark program is increasingly inappropriate for modern contexts, as it was designed in 2009, aimed specifically at datacentre computing rather than embedded.

Part of what the suite measures, for example, is the interrupt latency of a program, particularly relevant for automotive applications that only run in specific contexts. Expertise in this area is provided by Cesare Garlati of Hex Five Security.

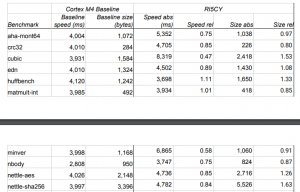

An example table shows the relative performance and code size of the RI5CY, an FPGA

implementation of the RISC-V RV32IMC instruction set, to the M4.

The overall performance is 93% of the M4—7% slower—with one geometric standard deviation being between 80% and 108%, and the code size is 105%—5% larger—with one geometric standard deviation being between 86% and 128%.

Neither the difference in speed, nor the difference in code size, is statistically significant.

Embench 0.5 is being developed by a committee of the free and open source silicon foundation. The committee aims to iteratively improve the benchmark with revisions every few months until it can release version 1.0, aiming for Q4 2020.

It plans to revisit the suite biannually to keep up to date, refreshing the programs to reflect requirements and preempt any workarounds.

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News

A very interesting article. If the investigation continues, the Embench 0.5 will be operational by the end of 2020, which will be a great step forward. This factor can be key in many industrial sectors.

regards