Large scale 2D antenna array systems will be key to the increase in spectral efficiency and network densification needed for 5G.

Manufacturers must find new ways to meet stringent requirements for commercial deployment.

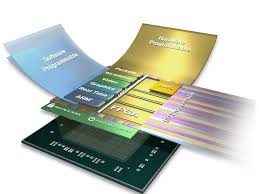

With the integration of high performance ADCs and DACs in an All Programmable SoC, radio and wireless backhaul units can now meet previously unattainable power and form factor requirements, while increasing channel density.

Additionally, RFSoC devices allow manufactures to streamline design and development cycles to meet 5G deployment timelines.

The integrated 16nm-based RF data conversion technology includes:

- Direct RF sampling for simplified analog design, greater accuracy, smaller form factor, and lower power

- 12-bit ADCs at up to 4GSPS, high channel count, with digital down-conversion

- 14-bit DACs at up to 6.4GSPS, high channel count, with digital up conversion

“Integrating RF signal processing into All Programmable SoCs enables our customers to dramatically change their systems architectures. It also continues the Xilinx imperative for continuous, breakthroughs in system integration,” says Xilinx’s Liam Madden, “this will effectively enable our 5G customers to commercially deploy highly differentiated, large-scale, massive-MIMO and millimeter-wave backhaul systems.”

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News